catalogue

1, Two interrupt events for C66x

2. Mapping to secondary events through CIC

2, Method of interrupt configuration

a,configuring the CorePac's INTC

2. Interrupt configuration of sysbios

1, Two interrupt events for C66x

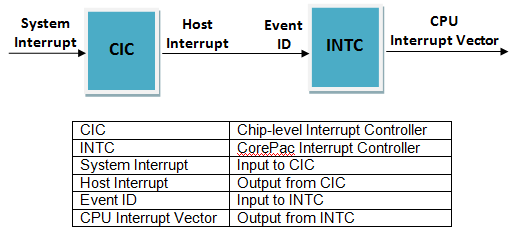

The CorePac interrupt controller allows 124 interrupts to be mapped to the DSP core and has events, as shown in the figure: events can be mapped separately

To the CPU, multiple events can also form a combination, and events can be mapped to the CPU.

At the same time, a CPU core has 16 interrupts, and 4-15 bits can mask configurable interrupts.

1. 98 primary events

Under SYSBIOS, HWI module can be used for direct configuration, and the hardware interrupt number can be queried from the interrupt manual.

If you do not run SYSBIOS, you need to configure the interrupt.

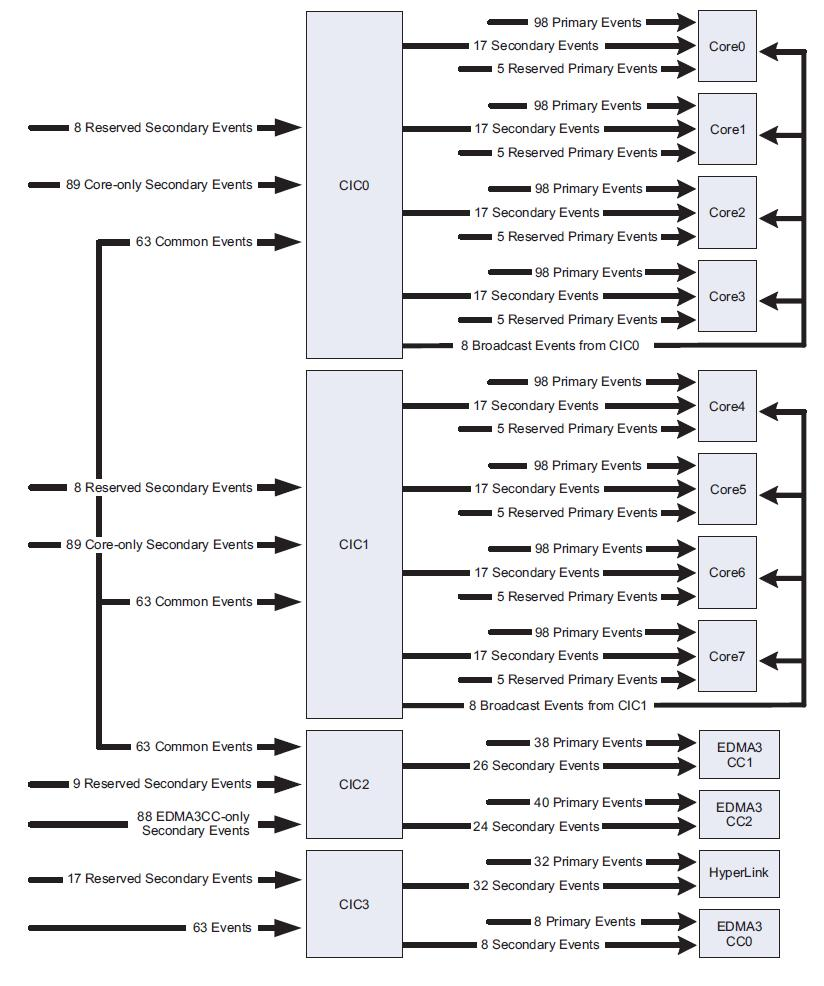

2. Mapping to secondary events through CIC

SYSBIOS does not support the direct mapping of CIC events to core interrupts, so first configure CIC and map system interrupt

It is Host interrupt. The Event id from Host interrupt to Event id is fixed, which can be queried in the manual; Next, perform the first step

Step.

2, Method of interrupt configuration

1.CSL method configuration

a,configuring the CorePac's INTC

Map Event ID63 to CPU interrupt 4

CSL_intcGlobalEnable() and CSL_intcGlobalNmiEnable() APIs

CSL_ The intcopen (...) API is an interrupt mapping. When the mapping is successful, the event will be saved to the interrupt and a valid handle will be returned.

CSL_intcPlugEventHandler(...) API binding event and interrupt functions

CSL_intcHwControl(...) API enable event

CSL_ The intcclose (...) API deallocates and releases events

b ,Configuring CIC

' pdk_C6678_x_x_x_xx\packages\ti\csl\example\cpintc 'you can learn more about CIC

c,Example

01

Note: host interrupt and channel in 6678 are one-to-one correspondence.

02

2. Interrupt configuration of sysbios

a. Create HWI thread

(refer to Sys BIOS tutorial for detailed methods, which will not be repeated)

Example event ID 10 is mapped to interrupt vector 5

b. Event Union

EventCombiner supports the combination of up to 32 events into one event. The output of EventCombiner can be connected to any configurable interrupt, and supports the combination of up to 32 * 4 events.

Support enable control of each event and interrupt function.

01

02

c,CpIntc

CpIntc manages CIC, which does not support interrupt nesting.

Turn on or off system and host interrupts,

system interrupts to host interrupts mapping (CIC)

host interrupts to HWIs, EventCombiner

There is a dispatch function for handling GEM hardware interrupts triggered by a system

interrupt. The Global Enable Register is enabled by default in the module startup function.

CpIntc APIs is 'ti.sysbios.family.c66.tci66xx.CpIntc'

Example

01

02