Second conversion

https://baike.baidu.com/item/%E7%A7%92/2924586

1s = 10 ^ 3MS (milliseconds) = 10 ^ 6 μ S (microsecond) = 10 ^ 9ns (nanosecond) = 10 ^ 12ps (picosecond) = 10 ^ 15fs (femtosecond) = 10 ^ 18as (attosecond) = 10 ^ 21zm (Ze second) = 10 ^ 24ym (per second)

Time unit: 1ns, 10fs accuracy

`timescale 1ns/10fs

Incomprehensible

https://www.cnblogs.com/jiu0821/p/4166192.html

1) Structures supported by all comprehensive tools: always, assign, begin, end, case, wire, tri, authly0, supply1, reg, integer, default, for, function, and, nand, or, nor, xor, xnor, buf, not, bufif0, bufif1, notif0, notif1, if, inout, input, instance, module, edge, position, operators, output, parameter. 2) Structures not supported by all comprehensive tools: time, defparam, $finish, fork, join, initial, delays, UDP, wait. 3) Some tools support structures that some tools do not support: casex, casez, want, triand, wor, trior, real, disable, forever, arrays, memories, repeat, task, while. Principles of establishing a comprehensive model To ensure the comprehensiveness of Verilog HDL assignment statements, the following points should be paid attention to during modeling:

(1) Do not use initial.

(2) Not used #10.

(3) Do not use loop statements with uncertain loop times, such as forever, while, etc.

(4) Do not use user defined primitives (UDP components)

(5) Try to design the circuit in synchronous mode.

(8) All internal registers should be able to be reset. When using FPGA to realize the design, the global reset end of the device should be used as the total reset of the system.

(12) Avoid mixing triggers triggered by rising and falling edges. Non integrable verilog statements 1,initial

2,events

3,real

4,time

5. force and release

6. Assign and deassign do not support the integration of assign or deassign of reg data type, and they support the integration of assign or deassign of wire data type.

7. fork join is not comprehensive. You can use non block statements to achieve the same effect.

8. Primitives supports the synthesis of gate level primitives and does not support the synthesis of non gate level primitives.

9. Table does not support the combination of UDP and table. 10. The sensitive list contains both posedge and negedge always @ (posedge CLK or negedge CLK) begin The end always block is not comprehensive. 11. The same reg variable is driven by multiple always blocks

12. The delay beginning with # delay cannot be integrated into hardware circuit delay. The integration tool will ignore all delay codes, but will not report an error.

For example: a=#10 b; Here #10 is the delay for simulation, which will be ignored by the synthesis tool during synthesis. That is to say, in synthesis, the above formula is equivalent to a=b;

13. Comparison with X and Z

Inertia delay and transmission delay

@The difference between and wait

Two concepts, but there are some similarities. Mainly the differences in usage@ It should be a trigger at a certain point in time. Wait seems to wait for a period of time.

In competitive relationships, the use of wait can mitigate events that are occasionally not triggered.

https://blog.csdn.net/qq_41894346/article/details/104964478

In Verilog, when a thread blocks an event and another thread triggers the event, competition occurs. If the trigger thread precedes the blocking thread, the trigger is invalid (the trigger is a zero width pulse).

Systemverilog introduces the triggered() function to detect whether an event has been triggered, including being triggered. The thread can wait for this result.

event a; //Use the keyword event to declare an event a

initial begin

#1;

->a;

end

initial begin

#1;

@a; //The first process triggers event a after 1ns, and the second process waits for a after 1ns. It may or may not wait, resulting in competition

end

initial begin

#1;

wait(a.triggered); //Using wait to wait for event a is different from using @ to wait

endExample 2

https://blog.csdn.net/Michael177/article/details/120807670

triggered() function, used to detect whether an event has been triggered, including being triggered. The thread can wait for this result instead of xx on the @ operator.

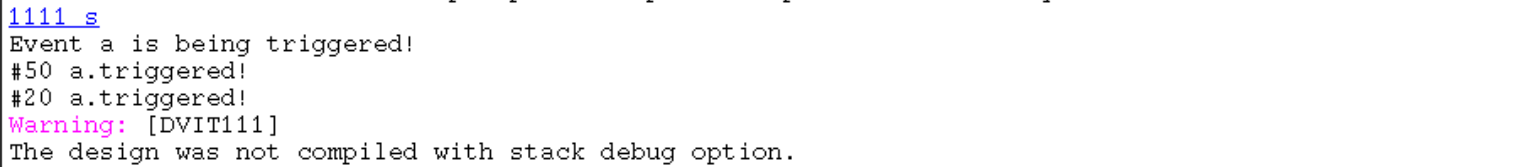

module event_test();

event a;

initial begin

#50;

->a;

$display("Event a is being triggered!");

end

initial begin

#20;

wait(a.triggered);

$display("#20 a.triggered!");

end

initial begin

#50;

wait(a.triggered);

$display("#50 a.triggered!");

end

initial begin

#60;

wait(a.triggered);

$display("#60 a.triggered!");

end

endmodule

parameter,interger,reg

https://blog.csdn.net/wuguozeng1989/article/details/46682125

1. Variables of type integer are used as signed numbers, while variables of type reg are used as unsigned numbers.

2. The bit width of integer is the number of bits of the word, and the minimum is 32 bits

https://blog.csdn.net/qq_16923717/article/details/81067096

3. parameter is a constant, not a variable, so its value cannot be modified at runtime, that is, it cannot be assigned in combinatorial logic or temporal logic.

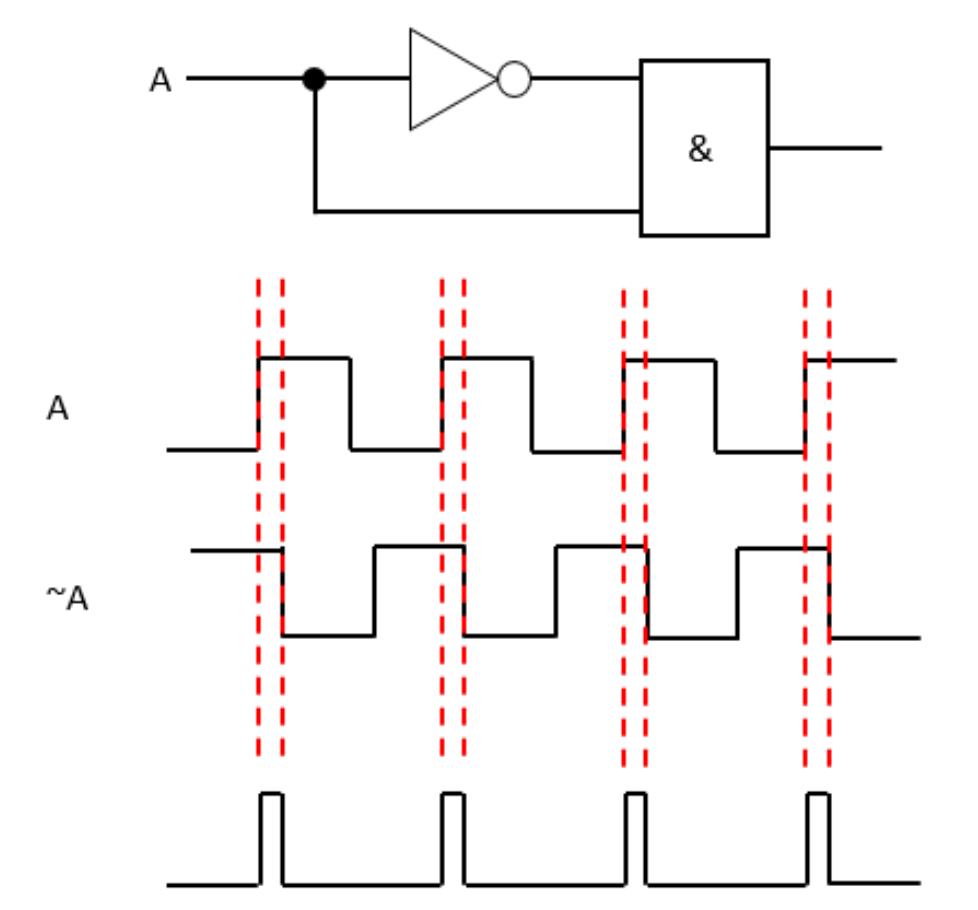

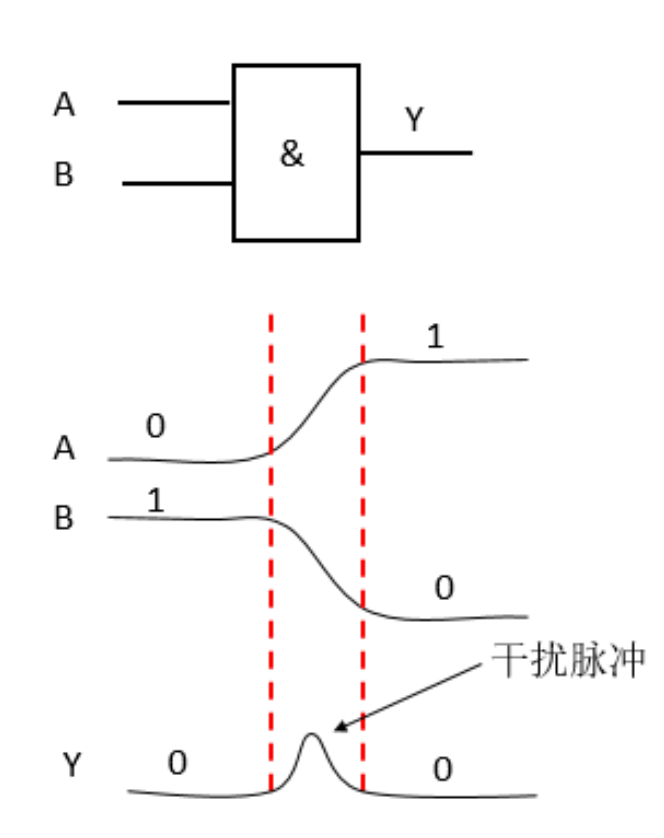

Competition and adventure

https://blog.csdn.net/wordwarwordwar/article/details/79829130

Because the signal is transmitted through different paths to reach a convergence point, there is a phenomenon of first and then, it is called competition, which is called Race in English;

The phenomenon of instantaneous error in circuit output caused by competition is called adventure, which is called Hazard or Risk in English.

Competition does not necessarily mean adventure, but when there is adventure, there must be competition.

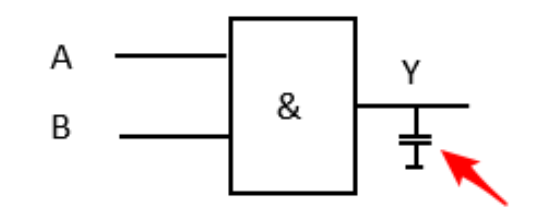

Solution:

1. Introduce blocking pulse and latch

2. Introduce strobe pulse and select after stabilization

3. Introduce filter capacitor.

4. Modify the logic design.

https://blog.csdn.net/yc16032399/article/details/100126361

RS latch

https://blog.csdn.net/kewei168/article/details/101141511

Truth table

R | S | Q |

|---|---|---|

0 | 0 | Q |

0 | 1 | 1 |

1 | 0 | 0 |

1 | 1 | X |

- When R=1, S=0 and the output is 0, so R is also called direct setting "0" end or "reset" end

- When R=0, S=1 and the output is 1, so S is also called direct setting "1" end or "setting" end

- When R=S=0, the output remains unchanged (it ensures that the circuit output can remain unchanged after RS is 0 (power off)

- RS is 1 at the same time. If it changes from the state that is 0 at the same time, an indefinite input state 01 or 10 will be generated in the middle, and an indefinite output will be generated and will not be used.

Makefile

Makefile is divided into two parts and explained one by one.

(1) The first part is as follows

CC=g++

sources:=$(wildcard *.c) $(wildcard *.cpp)

objects:=$(patsubst %.c,%.o,$(patsubst %.cpp,%.o,$(sources)))

dependence:=$(objects:.o=.d)

all: $(objects)

$(CC) $(CPPFLAGS) $^ -o $@

@./$@

%.o: %.c

$(CC) $(CPPFLAGS) -c $< -o $@

%.o: %.cpp

$(CC) $(CPPFLAGS) -c $< -o $@wildcard Indicates a wildcard, source Is all in the entire folder c Documents and h Variables composed of files. patsubst Represents a replacement,%Indicates any. First will source All in variable cpp Convert file name to o The file name, and then the modified variable, all c Convert file name to o File name, last composition object Variable. The equal sign on the next line represents the replacement relationship, which will object All in.o Replace file name with.d File name, consisting of dependence File name variable. make The first rule is executed by default. The first rule is named all,It relies on all object,All under this folder.o File. Before executing this statement, you should execute all the.o Corresponding rules when all.o After the rules of are met, the compilation process is executed. Among them $^Represents all dependent file names under this rule, $@Indicates the name of this compilation rule, i.e all. When this command is executed, a file named all Executable file. Later@Indicates that the command executed is not displayed (when executed) make When, all the actual commands executed are printed on the screen). CC For compiler, use=A variable that represents a deferred effect, using:=Represents an immediate variable. The use meaning of delayed variables is that CC After the reassignment, the result of the reassignment is displayed throughout the Makefile Effective in. %.o:%.c Represents each folder under the current folder.o File methods depend on each corresponding.c File. Then perform the build process. During generation, use $<Represents the first of the files that the method depends on (because sometimes the dependent content includes not only.c Documents, including.h Documents,.h Files are generally not written in the first position).

(2) The second part is as follows

include $(dependence)

define gen_dep

set -e; rm -f $@; \

$(CC) -MM $(CPPFLAGS) $< > $@.$$$$; \

sed 's,\($*\)\.o[ :]*,\1.o $@ : ,g' < $@.$$$$ > $@

rm -f $@.$$$$

endef

%.d: %.c

$(gen_dep)

%.d: %.cpp

$(gen_dep)

.PHONY: clean

clean:

rm -f all $(objects) $(dependence)

echo:

@echo sources=$(sources)

@echo objects=$(objects)

@echo dependence=$(dependence)

@echo CPPFLAGS=$(CPPFLAGS)use define and endef Macro definition to gen_dep Represents the following four lines of commands. set -e,This sentence tells bash If the execution result of any statement is not true You should exit instead of continuing down. rm -rf $@Indicates that the generated target file is deleted. include Indicates the introduction of an external file, which is similar in principle to C In language.c File. Here will be all.d Expand file rules. The reason for writing here instead of at the beginning is that the rule written at the beginning is the default rule, and writing at the beginning will overwrite the default rule. -M Show complete c File dependency on header file, generally used-MM Just display the part that does not contain the system header file.>The symbol represents a data redirection symbol that redirects data to $@.$$$$File. stay Makefile In the document, $A tag representing a variable, using $$Is real $Symbol. Four $Convert to two $Symbols, two $The symbol represents the of the process pid. Therefore, the data will be redirected to a suffix of.pid In the corresponding file. sed The comma is used as the separator in the replacement command of, s,g As the beginning and end, add a comma in the middle to replace the line. $*matching%.d Medium%The part represented by the wildcard is the first part of the data represented by the wildcard when the wildcard is used for the rule target. Then add parentheses and.o,And add several spaces and colons as the source of the replacement. The regular expression is divided into three parts, with parentheses as the first part,.o For the second part,[ :]*It is the third part. In the replacement target,\1 Represents the first part of the replaced source, and then adds.o And spaces and prerequisite names under the rule. The result of the replacement is stored in the target file. sed Some parts of the dependencies generated in the previous sentence are replaced and written to each prerequisite file. Replace with: target.o : target.c *.h Replace with: target.o target.d : target.c *.h. each target.d The generation of files depends on the corresponding target.c and*.h File. When.d If the file changes, execute the corresponding make Rules. Namely.d The file represents an alternate name. Subsequent%d:%c as well as%d:%cpp The required command is executed accordingly..d If the file is up-to-date, then.d The corresponding rule will not be executed. clean The same is true. When there is a clean The corresponding rule will not be executed. use.PHONY This effect can be removed so that it must be executed every time the command is selected. Subsequent statements are regular statements.