This is a VHDL course design completed at the end of October 2021. It is designed and assembled by yourself in the whole process. It is now archived and released as a record. You can also learn from this article to complete your own course design. (it is recommended to use the computer to read, and this article is modified)

Design of digital electronic clock based on VHDL language

[content abstract] digital electronic clock is a time recording device that uses digital display of seconds, minutes and hours. The functions and characteristics of the digital electronic clock are as follows: the clock source generates 1Hz clock pulse to provide the counting of "seconds"; Two hexadecimal counters are designed to count the "minute" and "second" signals, and a twenty-four hexadecimal counter to count the "hour" signal; Time correction through "hour" and "minute" correction circuits; The time reporting function and alarm function are realized through the combinational logic circuit, and the buzzer sends out a reminder. This course design uses Quartus II software, and the hardware language is VHDL.

[Key words] electronic clock counter digital electronic technology EDA VHDL

1 course design and scheme design

1.1 purpose and significance of EDA course design

Electronic technology is a highly practical course. Strengthening engineering training, especially the cultivation of skills, plays a very important role in cultivating the quality and ability of engineering personnel. In the undergraduate teaching of electronic information, electronic technology curriculum design is an important practical link. It includes the selection of topics, electronic circuit design, assembly, debugging and preparation of summary reports.

Through EDA course design, we should achieve the following two objectives: first, let students preliminarily master the test and design methods of EDA electronic circuits. That is, according to the design requirements and performance parameters, students consult literature, collect and analyze the performance of similar circuits, and make the circuit reach the performance index through practical activities such as assembly and debugging; Second, the curriculum design lays a good foundation for the subsequent graduation design. Graduation design is a systematic engineering design practice, and the focus of curriculum design is to enable students to gradually lead from the track of theoretical learning to practical application, gradually master the steps and methods of engineering design from the learned methods of qualitative analysis and quantitative calculation, understand the procedures and implementation methods of scientific experiment, and write the curriculum design report, Lay a foundation for engaging in technical work and writing scientific and technological reports and technical materials in the future.

one point two Learning objectives of this course design

1) Master the design, assembly and debugging methods of electronic clock.

2) Familiar with the use of Quartus II software.

3) Improve practical ability, learn to combine theoretical knowledge with practice, and give full play to the ability of individual and team cooperation.

one point three Design tasks and requirements

1) Clock display function, which can display "hour", "minute" and "second" in decimal system.

2) It has the function of calibrating hour, minute and second.

3) The whole point will automatically report the time. At the whole point, it will automatically sound.

4) With alarm function, you can set the alarm time and sound at that time.

2 basic implementation idea and system block diagram

two point one Basic implementation ideas

The timing function of the digital electronic clock is realized by three counters, in which the minute and second timing are 60 hexadecimal counting respectively, and the hour timing is 24 hexadecimal counter, which is connected by carry cascade.

The time calibration function of digital electronic clock is realized by three keys. The second time calibration is to press zero, and the branch time and time calibration are realized by long pressing the key to speed up the clock frequency.

The whole point time reporting function of digital electronic clock needs to detect whether the time reaches the whole point. If so, the speaker works; otherwise, the speaker does not work.

The alarm function of digital electronic clock needs three keys and three other counters, that is, minute and second timing are 60 hexadecimal counting respectively, and hour timing is 24 hexadecimal counter, but it is not connected in cascade mode. Three keys are connected to the counter, and the setting time is realized by long pressing the key. The implementation idea of alarm detection is similar to that of whole point detection.

The nixie tube of the digital electronic clock needs to display the normal time or alarm time. Therefore, a key can be added to switch the normal interface and alarm interface. The key can be used as the bit selection signal of one out of two selector. The nixie tube determines which time to display through the selector without affecting the timing of time.

two point two Overall circuit control logic

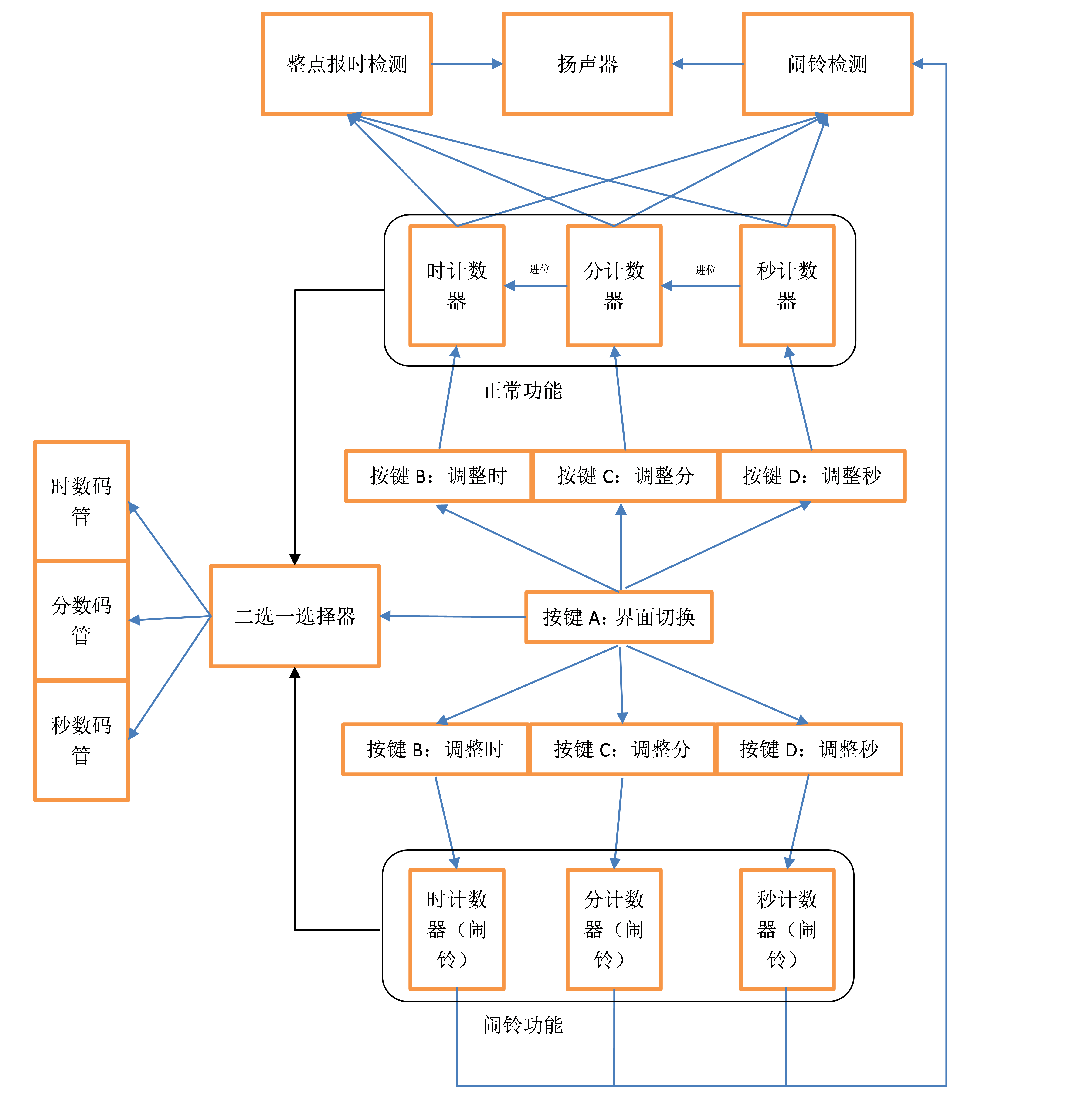

The overall logic block diagram of the circuit is shown in the figure above. Some explanations need to be made here:

A digital clock with basic functions such as timing, timing, timing and display is mainly composed of frequency divider, counter, display, timing, timing, alarm and other modules.

The original clock signal gets the second pulse through the frequency divider, and the second pulse is sent to the counter for counting. The counting results are decoded by the "hour", "minute" and "second" decoders, and the time is displayed on the display.

Key A is used to switch the interface, which can switch the normal interface and alarm interface. The keys B, C and D are used to adjust the hour, minute and second. When they are in the normal interface, they are used to calibrate the time. When they are in the alarm interface, they are used to adjust the alarm. Through A combinational logic module, you can distinguish the different functions of keys under different interfaces (limited to space, this module is not drawn in the figure). Therefore, the three keys have the function of multiplexing.

The timing module receives the output from the above three normal time counters, and the alarm module receives the output from the following three alarm time counters, which will continuously detect whether they meet the ring requirements.

3 module circuit design and simulation

three point one Frequency divider module

The function of frequency divider is to divide the original clock frequency into two frequencies. The former supplies the clock source of normal clock, and the latter supplies the clock source for setting alarm and timing.

3.1.1 code implementation

The implementation principle is that the output clock signal will flip once every N original clock cycles, so as to obtain a new clock frequency. The complete code is as follows:

[code 3-1 frequency divider]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; -- Frequency divider entity diver is port( clk: in std_logic; -- Original clock frequency clk0: out std_logic; -- Normal timing and frequency division clk1: out std_logic -- Set alarm and time division ); end diver; architecture a of diver is signal m_clk0: std_logic; signal m_clk1: std_logic; constant c_cnt_0: integer:= 10; constant c_cnt_1: integer:= 50; begin clk0 <= m_clk0; clk1 <= m_clk1; process(clk) variable cnt_0: integer range 0 to c_cnt_0; variable cnt_1: integer range 0 to c_cnt_1; begin if (clk'event and clk = '1') then cnt_0:= cnt_0 + 1; cnt_1:= cnt_1 + 1; if (cnt_0 = c_cnt_0) then m_clk0 <= not m_clk0; cnt_0:= 0; end if; if (cnt_1 = c_cnt_1) then m_clk1 <= not m_clk1; cnt_1:= 0; end if; end if; end process; end a;

3.1.2 simulation results

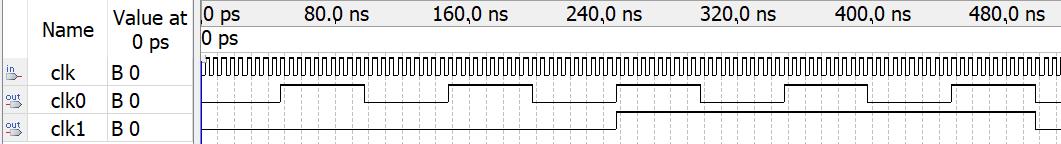

The simulation results of the software are as follows:

It can be seen that the original clock generates two different clock frequency signals after frequency division, which shows that the expected effect is achieved and the simulation is successful. However, the frequency division factor needs to be further adjusted in the subsequent commissioning stage.

three point two Counter module

The counters of clock and alarm are composed of a 24 hexadecimal counter and two 60 hexadecimal counters. Therefore, the clock and alarm counter are described in this section.

3.2.1 code implementation

The counter is an addition counter with asynchronous reset and synchronous enable. There are three inputs: input clock signal clk, asynchronous reset rst and synchronous enable en; The output terminal is one bit and ten bit binary numbers q0 and q1, and carry signal cout.

The following is the complete code of the second / minute counter:

[code 3-2 sec / min counter]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; -- Second timer entity count_sec is port( clk, rst, en: in std_logic; q0, q1: buffer std_logic_vector(3 downto 0); cout: out std_logic ); end count_sec; architecture a of count_sec is signal m_clk: std_logic; signal num0, num1: std_logic_vector(3 downto 0); begin cout <= '1' when (num0 = "1001" and num1 = "0101" and en = '1') else '0'; process (rst, clk) begin m_clk <= clk; if (rst = '0') then num0 <= "0000"; num1 <= "0000"; elsif (m_clk'event and m_clk = '0') then if (en = '1') then if (num0 = "1001") then num0 <= "0000"; if (num1 = "0101") then num1 <= "0000"; else num1 <= num1 + 1; end if; else num0 <= num0 + 1; end if; end if; end if; end process; q0 <= num0; q1 <= num1; end a;

The following is the complete code of the time counter:

[counter at code 3-3]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; -- Hour timer entity count_hour is port( clk, rst, en: in std_logic; q0, q1: buffer std_logic_vector(3 downto 0); cout: out std_logic ); end count_hour; architecture a of count_hour is signal m_clk: std_logic; signal num0, num1: std_logic_vector(3 downto 0); begin cout <= '1' when (num0 = "0011" and num1 = "0010" and en = '1') else '0'; process (rst, clk) begin m_clk <= clk; if (rst = '1') then num0 <= "0000"; num1 <= "0000"; elsif (m_clk'event and m_clk = '0') then if (en = '1') then if ((num0 = "0011") and (num1 = "0010")) then num0 <= "0000"; num1 <= "0000"; elsif (num0 = "1001") then num0 <= "0000"; num1 <= num1 + 1; else num0 <= num0 + 1; end if; end if; end if; end process; q0 <= num0; q1 <= num1; end a;

3.2.2 simulation results

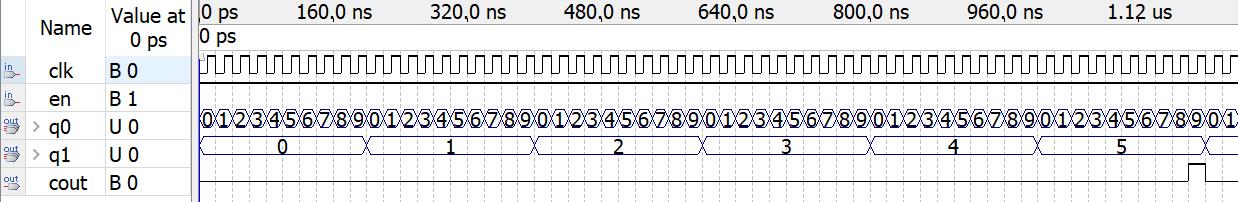

The following are the simulation results of second counter and minute counter (base 60 counter):

The following is the simulation result of the time counter (24 digit counter):

It can be seen that both of them have achieved the expected effect and the simulation is successful.

three point three Timing module

The specific realization of the time calibration function is that when the adjustment key is pressed for a long time, the clock frequency (i.e. counting frequency) will accelerate. When the clock jumps to the desired time, release the key, so as to complete a time calibration.

The realization principle of the timing function is very ingenious, which is realized through a two-out-of-one selector. The bit selection signal s is connected to the adjustment key. The two signals a and b are the carry signal from the low-level counter and the clock signal with faster frequency respectively, and the output end is connected to the carry signal of the counter.

In this way, when the key is not pressed, the selector outputs a signal, and the counter counts at the normal frequency; When the key is pressed, the selector outputs b signal. At this time, the counter counts at a faster frequency for the user to calibrate the time.

3.3.1 code implementation

The essence of the time calibration module is one out of two selector. The complete code is as follows:

[code 3-4 timing module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21a IS PORT ( a, b, s: IN STD_LOGIC; y : OUT STD_LOGIC ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ;

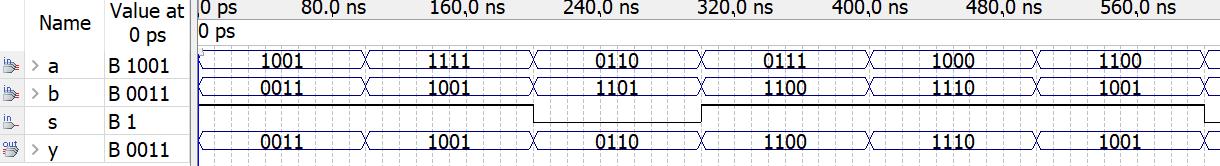

3.3.2 simulation results

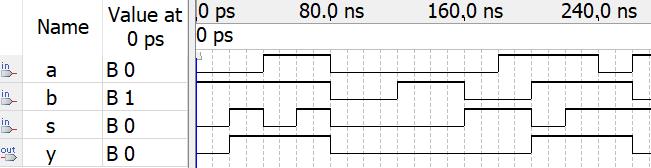

The simulation results of the software are as follows:

It can be seen that it has achieved the expected effect and the simulation is successful.

three point four Time reporting module

The specific implementation of the time reporting module is that when it is detected that the minute reaches 59 and the second reaches 53, 55, 57 and 59, the buzzer rings once respectively.

3.4.1 code implementation

The input terminal is the minute and second from the clock counter, and the output terminal is connected to the buzzer. The implementation of the code only needs to detect whether it meets the conditions that the minute reaches 59 and the second reaches 53, 55, 57 and 59. If so, the buzzer signal is high level, otherwise it is low level. The complete code is as follows:

[code 3-5 time reporting module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity baoshi is port ( min0 ,min1 , sec0, sec1 :in std_logic_vector ( 3 downto 0 ); speak: out std_logic ); end baoshi; architecture cml of baoshi is begin speak <= '1' -- min1=5, min0=9, sec1=5 and sec0=3, sec0=5, sec0=7, sec0=9 when (min1="0101" and min0 ="1001" and sec1="0101")and ( sec0="0011" or sec0 ="0101" or sec0 ="0111" or sec0="1001") else '0'; end cml;

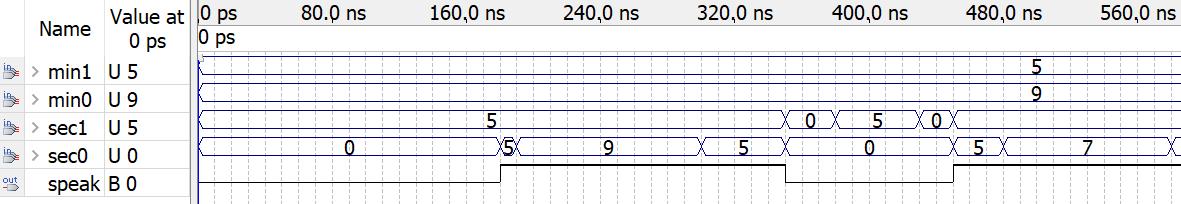

3.4.2 simulation results

The simulation results of the software are as follows:

It can be seen that it has achieved the expected effect and the simulation is successful.

three point five Mode switching module (key multiplexing module)

As mentioned earlier, the system we designed has three keys to adjust the hour, minute and second. Since the system has two modes, if each mode is equipped with three keys, it will be somewhat redundant (a total of six keys are required).

In order to reduce the number of keys, we hope that the three keys can set the normal time and alarm time in different modes, which is called "key reuse". Another advantage of this is that you don't have to worry about touching the alarm button by mistake in the state of normal display time. In order to realize the above functions, a logic circuit needs to be designed to distinguish whether to adjust the normal time or the alarm time.

3.5.1 code implementation

The input terminal is the signal s from the mode switching key and the time adjustment key. There are two output terminals, one connected to the part s1 of the normal time and the other connected to the part s2 of the alarm time. The realization idea is: when s is high, s2 passes and s1 is shielded. At this time, press key to adjust s2; When s is low, s1 passes and s2 is shielded. At this time, press key to adjust s1. Through the logic table, it is easy to get the following code:

[code 3-6 mode switching module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity switch is port( key, s: in std_logic; s1, s2: out std_logic ); end switch; architecture a of switch is begin s1 <= key and (not s); s2 <= key and s; end a;

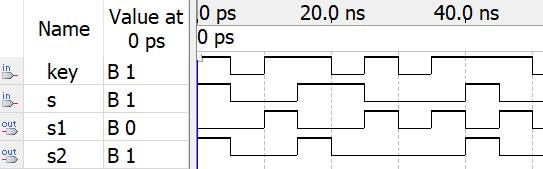

3.5.2 simulation results

The simulation results of the software are as follows:

It can be seen that it has achieved the expected effect and the simulation is successful.

three point six Mode state maintenance module

Because we hope that when we press the switch button, the mode state will switch and remain unchanged, we use T trigger to process the key signal. When the input signal from the key is high, the output signal q will flip the signal once; When the input signal from the key is low, the output signal q state remains unchanged.

3.6.1 code implementation

The input terminal has clock clk and signal T, and the output terminal is signal q. When the rising edge of the clock comes, if t is high level, the signal q turns over once; Otherwise, the signal q remains unchanged. The complete code is as follows:

[code 3-7 mode state maintenance module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; Use IEEE.STD_LOGIC_ARITH.ALL; Use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY trigger IS port (t, clk: in std_logic; q: out std_logic); end entity; architecture bhv of trigger is signal temp: std_logic; begin process(clk, t) begin if clk'event and clk='1' then if t='1' then temp <= not temp; else temp <= temp; end if; end if; q <= temp; end process; end bhv;

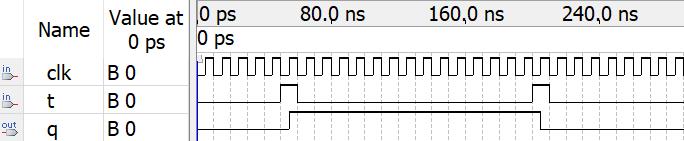

3.6.2 simulation results

The simulation results of the software are as follows:

It can be seen that it has achieved the expected effect and the simulation is successful.

three point seven Alarm detection module

The specific implementation of the alarm detection module is that when the detection time, minutes and seconds reach the preset time, the buzzer rings once.

3.7.1 code implementation

The input terminal is the min/hour counter from the clock and the amin/ahour counter from the alarm, and the output terminal is connected to the buzzer. When the detection time, minute and second reach the preset time, the buzzer rings once. The complete code is as follows:

[code 3-8 alarm detection module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity alarm is port( --sec0, sec1: in std_logic_vector(3 downto 0); min0, min1: in std_logic_vector(3 downto 0); hour0, hour1: in std_logic_vector(3 downto 0); --asec0, asec1: in std_logic_vector(3 downto 0); amin0, amin1: in std_logic_vector(3 downto 0); ahour0, ahour1: in std_logic_vector(3 downto 0); speak: out std_logic ); end alarm; architecture a of alarm is begin speak <= '1' when(min0=amin0 and min1=amin1 and hour0=ahour0 and hour1=ahour1) else '0'; end a;

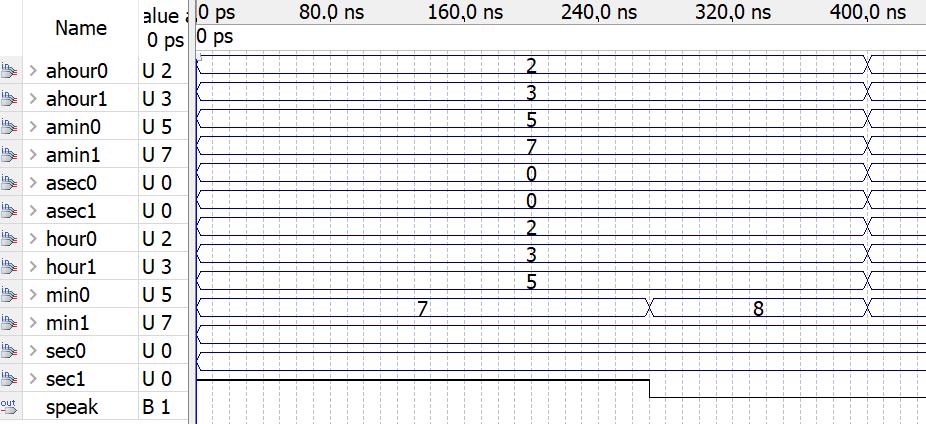

3.7.2 simulation results

Assuming that the alarm is set to 23:57:00 and the real time transitions from 23:57:00 to 23:58:00, the simulation results are as follows:

It can be seen that when the real time reaches 23:57:00, the speak is high level, and the buzzer works at this time; When the real time reaches 23:58:00, the speak is low level, and the buzzer does not work at this time, indicating that the expected effect is achieved and the simulation is successful.

three point eight Nixie tube display switching module

The function of the module is that the nixie tube can switch and display the normal time and alarm time through one out of two selector.

3.8.1 code implementation

This is a one out of two selector. There are three input signals. The bit selection signal comes from the mode switching button, and the other two are a and b, which come from the outputs q0 and q1 of the normal counter and the alarm counter respectively. The complete code is as follows:

[code 3-9 nixie tube display switching module]LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mmux21a IS PORT ( a, b: in std_LOGIC_vector (3 downto 0); s: IN STD_LOGIC; y : OUT std_LOGIC_vector (3 downto 0) ); END ENTITY mmux21a; ARCHITECTURE one OF mmux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ;

3.8.2 simulation results

The simulation results of the software are as follows:

It can be seen that it has achieved the expected effect and the simulation is successful.

4 top level circuit design, simulation and debugging

four point one Top level circuit design

After each module has been designed, simulated and achieved the expected effect, instantiate the module in the top-level file, and then connect it in a certain way. The following code defines the input and output ports of the whole system:

[code 4-1 top level circuit input / output port definition]entity clock_top_1 is port( clk: in std_LOGIC; --Clock source key_sec, key_min, key_hour: in std_LOGIC; --Timing setting/Alarm setting button sec0, sec1: buffer std_logic_vector(3 downto 0); --Display time min0, min1: buffer std_logic_vector(3 downto 0); --Display score hour0, hour1: buffer std_logic_vector(3 downto 0); --Display seconds key_shift: in std_LOGIC; --Switching function speak: out std_LOGIC --Ring the bell at the hour/Alarm ring ); end clock_top_1;

4.1.1 clock source

Create two signals to provide normal_clk and fast_clk respectively. The excerpt code is as follows:

[code 4-2 frequency divider instantiation]signal normal_clk, fast_clk : std_LOGIC; --------frequency division--------- U1: diver port map (clk=>clk, clk0=>normal_clk, clk1=>fast_clk);

4.1.2 normal time counting part

Define the signal, which is used for the display signal of nixie tube (sec0_n, sec1_n, min0_n, min1_n, hour0_n, hour1_n) (but it is not really displayed, because the mode switching module is also used to determine which interface to display); Define two carry signals (min_clk, hour_clk) to provide the clock of the next stage counter; The three counters are cascaded, and the carry signal is used as the clock source of the next counter.

Note that except the rst terminal of the second counter, all other counters are connected to the low level (the reset terminal is valid for the high level), because the timing mode of the second counter is only the reset mode. The excerpt code is as follows:

[code 4-3 normal time counting part instantiation]signal min_clk, hour_clk : std_LOGIC; signal sec0_n, sec1_n, min0_n, min1_n, hour0_n, hour1_n: std_logic_vector(3 downto 0); --------Normal time counter--------- U2: count_sec port map (clk=>normal_clk, rst=>key_sec_n, en=>'1', q0=>sec0_n, q1=>sec1_n, cout=>sec_cout); U3: count_min port map (clk=>min_clk, rst=>'0', en=>'1', q0=>min0_n, q1=>min1_n, cout=>min_cout); U4: count_hour port map (clk=>hour_clk, rst=>'0', en=>'1', q0=>hour0_n, q1=>hour1_n);

4.1.3 timing part

The bit selection signal s is connected to the adjustment keys (key_min_n and key_hour_n). The two signals a and b are the carry signals (sec_cout and min_cout) and the clock signal with faster frequency (fast_clk) from the low-level counter respectively, and the output end is connected to the carry signals (min_clk and hour_clk) of the counter. The excerpt code is as follows:

[code 4-4 timing part instantiation]signal key_sec_n, key_min_n, key_hour_n: std_LOGIC; --------Timing--------- U5: mux21a port map (a=>sec_cout, b=>fast_clk, s=>key_min_n, y=>min_clk); U6: mux21a port map (a=>min_cout, b=>fast_clk, s=>key_hour_n, y=>hour_clk);

4.1.4 alarm setting part

Three key signals (key_sec_a, key_min_a, key_hour_a) are defined to set the alarm time; The display signal (min0_a, min1_a, hour0_a, hour1_a) for nixie tube is defined.

The connection method of this part is similar to that of the normal time counting part. The difference is that the rst terminal of the three counters is low level, and the en terminal is connected with the key signal, which counts the number in the high-level state. The excerpt code is as follows:

[code 4-5 alarm setting part instantiation]signal sec0_a, sec1_a, min0_a, min1_a, hour0_a, hour1_a: std_logic_vector(3 downto 0); signal key_sec_a, key_min_a, key_hour_a: std_LOGIC; --------Alarm counter--------- U17: count_sec port map (clk=>fast_clk, rst=>'0', en=>key_sec_a, q0=>sec0_a, q1=>sec1_a); U18: count_min port map (clk=>fast_clk, rst=>'0', en=>key_min_a, q0=>min0_a, q1=>min1_a); U19: count_hour port map (clk=>fast_clk, rst=>'0', en=>key_hour_a, q0=>hour0_a, q1=>hour1_a);

4.1.5 mode switching part

The T trigger is used to maintain the mode state, which is exemplified as follows:

[code 4-6 T trigger instantiation]signal key_shift1: std_LOGIC; --------Mode state hold-------- U21: trigger port map (clk=>clk, t=>key_shift, q=>key_shift1);

The input terminal is the mode switching key (key_shift1) and the signal s (key_sec, key_min, key_hour) of the time adjustment key. There are two output terminals, one connected to the normal time part s1 (key_sec_n, key_min_n, key_hour_n) and the other connected to the alarm time part s2 (key_sec_a, key_min_a, key_hour_a). The excerpt code is as follows:

[code 4-7 mode switching partial instantiation]--------Mode switching (three key multiplexing)--------- U8: switch port map (key=>key_sec, s=>key_shift1, s1=>key_sec_n,s2=>key_sec_a); U9: switch port map (key=>key_min, s=>key_shift1, s1=>key_min_n,s2=>key_min_a); U10: switch port map (key=>key_hour, s=>key_shift1, s1=>key_hour_n, s2=>key_hour_a);

4.1.6 nixie tube display switching part

After distinguishing the hour, minute and second outputs of the alarm and the normal time part, this part selects to display one of the two outputs. The excerpt code is as follows:

[code 4-8 example of nixie tube display switching part]--------Nixie tube display switching (one out of two)--------- U11: mmux21a port map (s=>key_shift1, a=>sec0_n, b=>sec0_a, y=>sec0); U12: mmux21a port map (s=>key_shift1, a=>sec1_n, b=>sec1_a, y=>sec1); U13: mmux21a port map (s=>key_shift1, a=>min0_n, b=>min0_a, y=>min0); U14: mmux21a port map (s=>key_shift1, a=>min1_n, b=>min1_a, y=>min1); U15: mmux21a port map (s=>key_shift1, a=>hour0_n, b=>hour0_a, y=>hour0); U16: mmux21a port map (s=>key_shift1, a=>hour1_n, b=>hour1_a, y=>hour1);

4.1.7 whole point detection and alarm detection

Because the buzzer has two input sources, one is from the whole point time reporting and the other is from the alarm, or gate is introduced to solve the conflict between the two. The excerpt code is as follows:

[code 4-9 speaker selection code]signal speak_a, speak_zd: std_LOGIC; --Alarm(a)/Whole point(zd) --------speaker-------- speak <= speak_a or speak_zd;

The instantiation codes of whole point detection and alarm detection are as follows:

[code 4-10 instantiation of whole point detection and alarm detection]--------Whole point detection--------- U7: baoshi port map (min0=>min0, min1=>min1, sec0=>sec0, sec1=>sec1, speak=>speak_zd); --------Alarm detection--------- U20: alarm port map (min0=>min0_n, min1=>min1_n, hour0=>hour0_n, hour1=>hour1_n, amin0=>min0_a, amin1=>min1_a, ahour0=>hour0_a, ahour1=>hour1_a, speak=>speak_a );

So far, the instantiation and connection of all modules have been completed.

four point two Top level circuit simulation

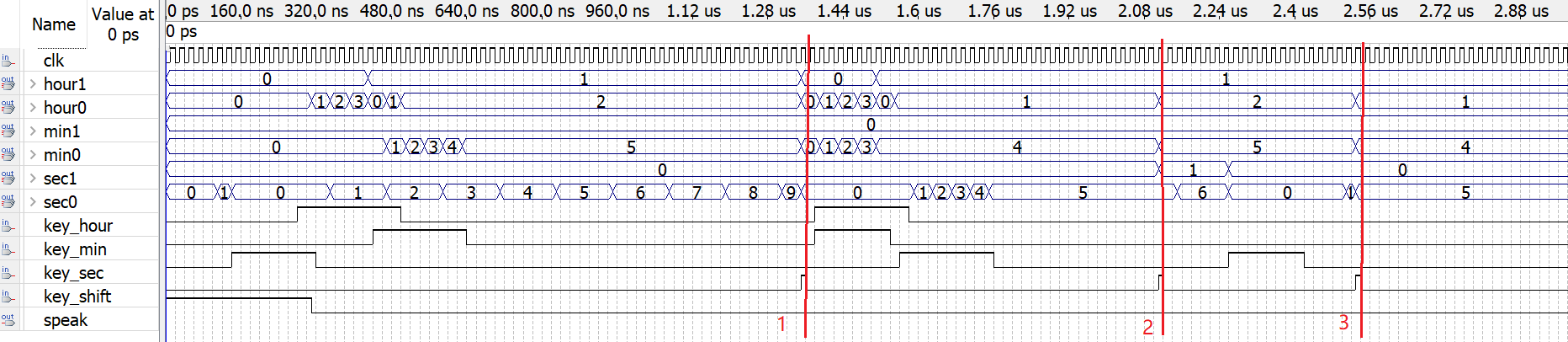

The simulation results using software are as follows:

From left to right:

(1) The first part in the figure tests the timing module. When the normal time interface is displayed, when the time calibration key and the branch time key are pressed, the counting frequency of minute and hour is accelerated. After releasing the key, the counter counts normally. At the same time, at the beginning, because it is the whole point, speak is a high level.

(2) The second part in the figure tests the alarm module. Press the key_shift and release it. The nixie tube will switch the display time of the alarm. When the time calibration key and the branch time key are pressed, the minute and hour counters will start counting. Release the timing key and the counter stops counting.

(3) in the third part of the picture, press the toggle button again and find that the digital tube is switched to normal time, and the alarm time before the alarm does not affect the count of normal time.

(4) In the last part of the figure, press the switch button again to enter the alarm mode. It is found that the nixie tube displays the previously adjusted alarm time.

Overall, the simulation results basically meet the expectations.

four point three Top level circuit commissioning

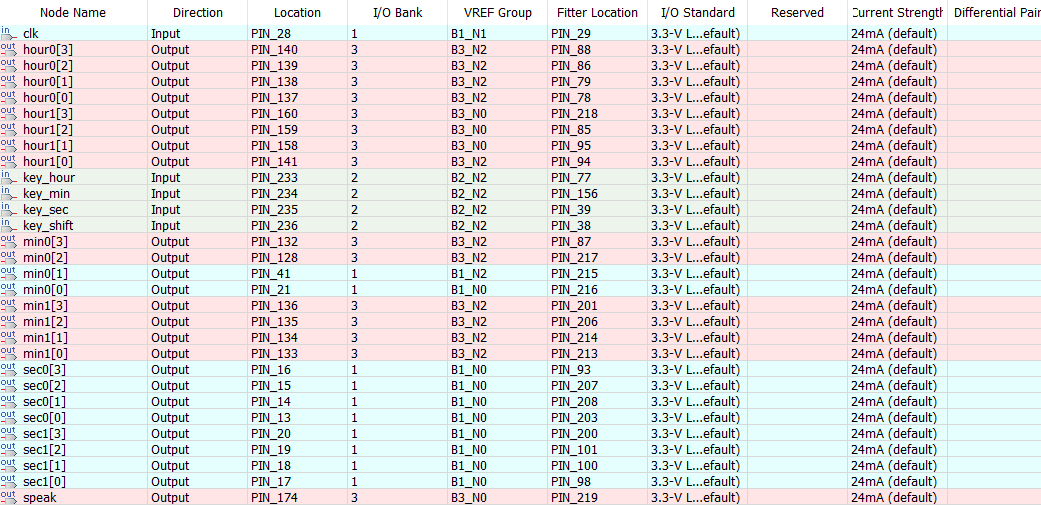

4.3.1 pin assignment

Pin locking is shown in the figure below:

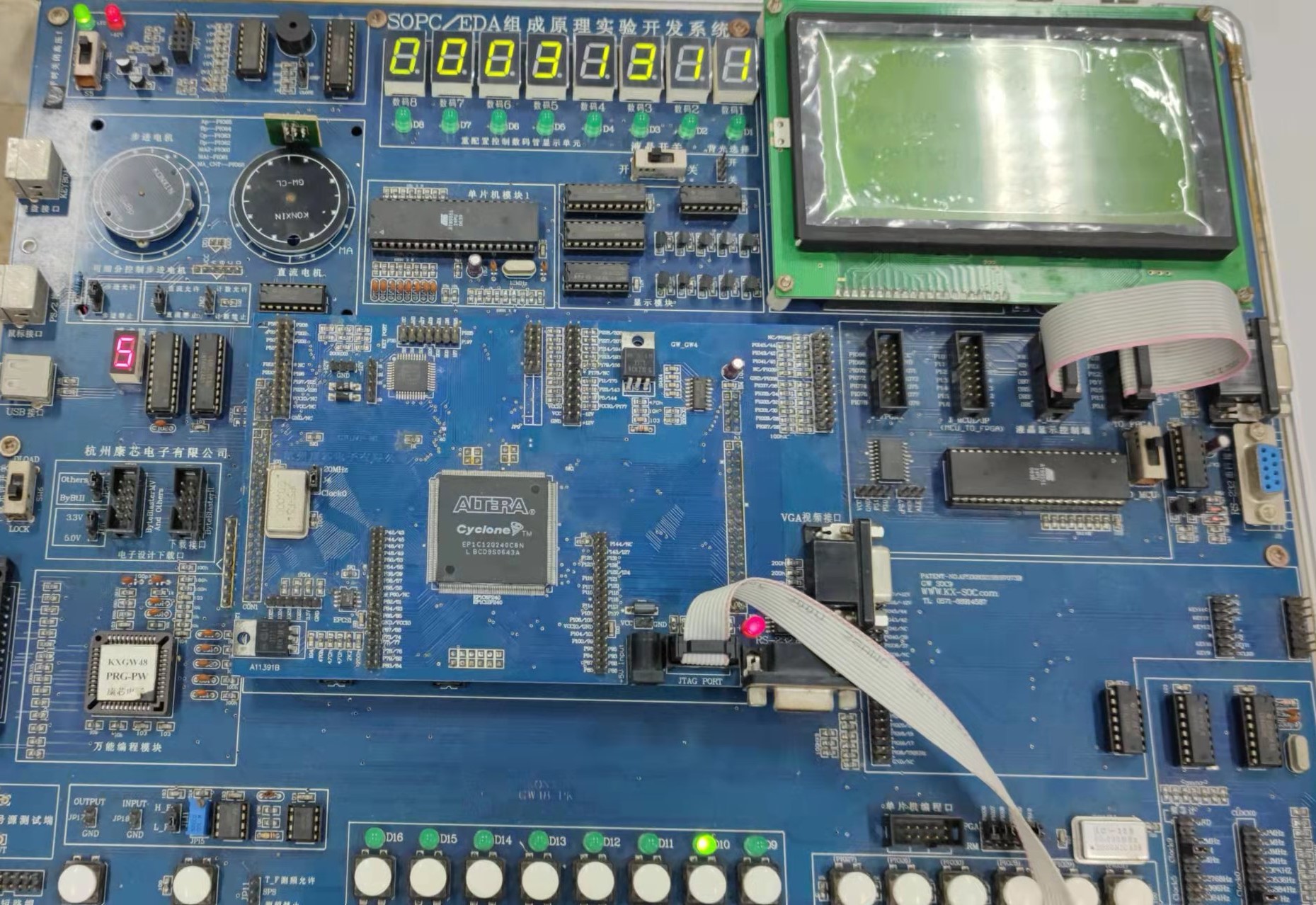

4.3.2 commissioning results

Download the program and conduct hardware test. The following figure shows the experimental phenomena during debugging:

Through a series of tests, we can count the time, adjust the time, ring the time and alarm. The experimental phenomenon is basically in line with the expectation.

5 Summary

five point one Defects and deficiencies

The course design has the following defects and deficiencies:

(1) The function of stopwatch is not realized, and the function of digital clock is not perfect;

(2) The design method of adjusting the time is not very good. Our scheme is to press the key, and the counting frequency will be accelerated. Later, after the teacher's reminder, in fact, the key can be directly connected to the next level counter, so that the time can be adjusted by pressing the key once. Obviously, this scheme is more concise;

(3) The alarm sounds only once, and the sound is very low.

What we didn't expect (or didn't notice) was that the buttons on the laboratory board had the function of state keeping, but we specially designed a module to achieve this function, which affected the final experimental effect. Unfortunately, due to the time relationship, it can not be perfect. In short, although the main functions have been realized, we are not particularly satisfied with the course design.

5.2 experience

Through the course design of digital analog circuit, from the first topic selection to the end of the final simulation, we have a deeper grasp of the principle and process of digital clock design. Although the topics given by the subject are relatively simple, it is inevitable that we have no way to start at the beginning. After all, curriculum design is different from experimental courses. We need to think about and design and practice code and logic diagram ourselves. The basic courses and experiments we learn usually combine theory with practice in this practice. It can not only consolidate the theoretical knowledge we have learned, but also improve our electronic circuit design level, but also strengthen our ability to comprehensively analyze and solve problems, and further cultivate our experimental skills and practical ability, Inspire our innovative consciousness and innovative thinking.

When we started the design, we focused on logic, divided the whole system into multiple modules according to different functions, broke them one by one, and finally integrated them. This is also an important method learned from this course. So after that, we calm down. By looking up the textbooks and extracurricular materials, plus the tips given by the instructor, we carefully analyzed the topic and thought about it. After we helped each other and expressed our opinions, we quickly completed the topic.

After several weeks of VHDL course design, we finally made a digital clock circuit. Although the process is difficult, the excitement can not be expressed in words. In the whole process of circuit design, I gradually strengthened my understanding and application ability of digital circuit and EDA design, and had a better summary and understanding of textbook knowledge and previous knowledge. Through this design, I deeply realized the difference between theory and practice, and understood the significance of the combination of theoretical knowledge and practice. Only when we do it ourselves and put the theory into practice, can we internalize the theoretical knowledge into our own part. In this process, my practical ability and mastery of theoretical knowledge have been greatly improved, which will lay a solid foundation for my future study and work. Finally, thank you for your advice and help!

appendix

Module list

| Module name | function | number |

|---|---|---|

| diver | Frequency divider | 1 |

| count_hour | Time counter | 2 |

| count_min | Sub counter | 2 |

| count_hour | Time counter | 2 |

| mux21a | One out of two selector (for timing module) | 2 |

| mmux21a | One out of two selector (for nixie tube display) | 6 |

| baoshi | Whole point detection | 1 |

| alarm | Alarm detection | 1 |

| switch | Mode switching | 3 |

| trigger | T flip-flop | 1 |

Total number of modules: 21

reference

[1] Yan Shi, editor in chief. Fundamentals of digital electronic technology [M]. Version 6. Beijing: Higher Education Press, 2016

[2] Yan Shi, Wang Hong, ed. basic learning guidance and problem solving of digital electronic technology [M]. Version 6. Beijing: Higher Education Press, 2016

[3] Pan song, Huang Jiye. Practical course of EDA Technology: VHDL version [M]. Version 6. Beijing: Science Press, 2018

[4] Jiang Guoqiang. Modern digital circuit and system design: VHDL version [M]. 6 th Edition. Beijing: Electronic Industry Press, 2018

[5] Liu Binghai, ed. learning electronic circuit design from scratch [M]. Beijing: Chemical Industry Press, 2019