summary:

Why a watchdog?

In the microcomputer system composed of single chip microcomputer, the work of single chip microcomputer is often disturbed by external electromagnetic field, resulting in the running and flying of the program and falling into a dead cycle. The normal operation of the program is interrupted, and the system controlled by single chip microcomputer cannot continue to work, which will lead to the stagnation of the whole system and unpredictable consequences, Therefore, considering the real-time monitoring of the running state of single chip microcomputer, a module or chip specially used to monitor the running state of single chip microcomputer program is produced, commonly known as "watchdog".

The independent watchdog (IWDG) is driven by a dedicated low speed clock (LSI), which is still valid even if the master clock fails.

The independent watchdog is suitable for the situation where the watchdog is required to work completely independently outside the main program and has low requirements for time accuracy.

Function introduction:

- Write 0xCCCC in the key value register (IWDG_KR) to start enabling the independent watchdog. At this time, the counter starts to decrease from its reset value 0xFFF. When the counter value counts to the tail value 0x000, a reset signal (IWDG_RESET) will be generated.

- Whenever in the key value register iwdg_ When 0xAAAA (commonly referred to as dog feeding) is written in Kr, the value of automatic reload register IWDG_RLR will be reloaded into the counter to avoid watchdog reset.

If the program is abnormal, the dog cannot be fed normally, so the system resets.

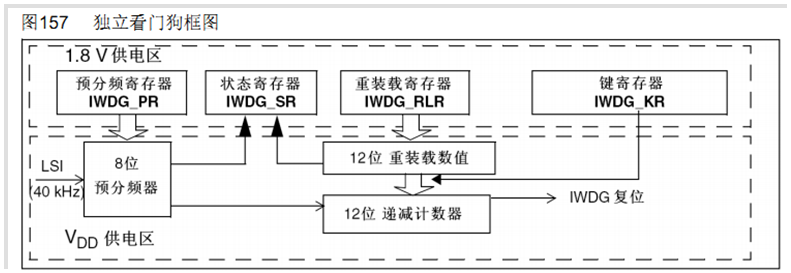

The program block diagram is as follows:

- Key value register IWDG_KR: 0~15 bits valid

- Prescaler register IWDG_PR: 0 ~ 2 bits valid. (with write protection function, write protection shall be cancelled before operation)

- Reload register IWDG_RLR: 0 ~ 11 bits valid. (with write protection function, write protection shall be cancelled before operation)

- Status register IWDG_SR: 0 ~ 1 bits valid

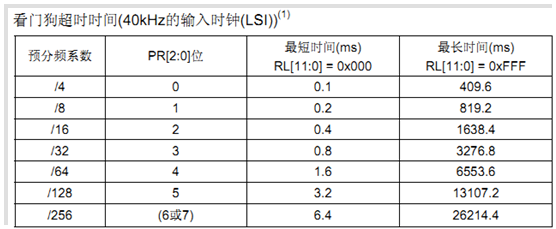

Independent watchdog timeout:

Overflow time calculation:

Tout=((4×2^prer) ×rlr) /40 (M3)

(prer is the frequency division coefficient)

The clock frequency LSI=40K, and a watchdog clock cycle is the shortest timeout time.

Maximum timeout = (maximum value of IWDG_RLR register) X watchdog clock cycle.

IWDG independent watchdog operation library function:

void IWDG_WriteAccessCmd(uint16_t IWDG_WriteAccess);//Cancel write protection: 0x5555 enable void IWDG_SetPrescaler(uint8_t IWDG_Prescaler);//Set prescaler coefficient: write PR void IWDG_SetReload(uint16_t Reload);//Set reload value: write RLR void IWDG_ReloadCounter(void);//Feed dog: write 0xAAAA to KR void IWDG_Enable(void);//Enable watchdog: write 0xCCCC to KR FlagStatus IWDG_GetFlagStatus(uint16_t IWDG_FLAG);//Status: reload / prescaled update COPY

Operation steps of independent watchdog:

① Cancel register write protection:

IWDG_WriteAccessCmd();

② Set the prescaled coefficient of the independent watchdog to determine the clock:

IWDG_SetPrescaler();

③ Set the watchdog reload value to determine the overflow time:

IWDG_SetReload();

④ Enable watchdog

IWDG_Enable();

⑤ App feed dog:

IWDG_ReloadCounter();

Overflow time calculation:

Tout=((4×2^prer) ×rlr) /40 (M3)

Experiment code:

iwdg.h:

#ifndef __WDG_H #define __WDG_H #include "sys.h" void IWDG_Init(u8 prer,u16 rlr); void IWDG_Feed(void); #endif COPY

iwdg.c:

#include "wdg.h"

//Initialize independent watchdog

//prer: frequency division number: 0 ~ 7 (only the lower 3 bits are valid!)

//Frequency division factor = 4*2^prer But the maximum value can only be 256!

//rlr: reload register value: the lower 11 bits are valid

//Time calculation (approximate): Tout=((4*2^prer)*rlr)/40 (ms)

void IWDG_Init(u8 prer,u16 rlr)

{

IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable); //Enable register IWDG_PR and iwdg_ Write operation of RLR

IWDG_SetPrescaler(prer); //Set IWDG prescaled value: set IWDG prescaled value to 64

IWDG_SetReload(rlr); //Set IWDG reload value

IWDG_ReloadCounter(); //Reload the IWDG counter according to the value of the IWDG reload register

IWDG_Enable(); //Enable IWDG

}

//Hey, independent watchdog

void IWDG_Feed(void)

{

IWDG_ReloadCounter();//reload

}

COPYmain.c:

#include "led.h"

#include "delay.h"

#include "key.h"

#include "sys.h"

#include "usart.h"

#include "wdg.h"

int main(void)

{

delay_init(); //Delay function initialization

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2); //Set NVIC interrupt packet 2: 2-bit preemption priority and 2-bit response priority

uart_init(115200); //The serial port is initialized to 115200

LED_Init(); //Initialize the hardware interface to the LED

KEY_Init(); //Key initialization

delay_ms(500); //Visible

IWDG_Init(4,625); //The number of and frequency division is 64, the overload value is 625, and the overflow time is 1s

LED0=0; //Lighting LED0

while(1)

{

if(KEY_Scan(0)==WKUP_PRES)

{

IWDG_Feed();//If wk_ Press up to feed the dog

}

delay_ms(10);

};

}

COPYExperimental phenomena:

The led light flashes continuously because the dog feeding program is not executed and STM32 is constantly reset.

When wk is pressed continuously_ When the up key is in the up position, the led lamp is in a stable luminous state.

This article is reproduced from: http://blog.bools.cn/archives/1377

Welcome to pay attention to official account, get more hardware learning dry cargo!

What can we offer you?

Technical guidance: C + +, Java, embedded software / hardware

Project counseling: software / hardware projects, large factory training projects

Employment counseling: the whole process of employment counseling and technical entrepreneurship support

Connecting enterprise HR: cultivating and transporting high-quality talents