1.sequence basic operation symbols

| Symbol | meaning |

|---|

| ## | Symbol used to indicate periodic delay |

1.##n Indicates in n After two clock cycles,##0 means in the current cycle, i.e. overlapping cycle

//One cycle after a is pulled up, b is also pulled up

sequence a_b

@(posedge clk) a ##1 b

endsequence

2.##[min:max] indicates the clock cycle delay within a range. Min and Max must be non negative numbers, and the sequence will match at the earliest time in the time window from min to max

//a 1 cycle or 2,3,4,5 cycles after pulling up, b pulling up

sequence a_b

@(posedge clk) a ## [1:5] b

endsequence

3.$Used to represent the period of infinity(Before the end of the simulation),However, this is generally not recommended because it will increase the burden on the simulation evaluation sequence

sequence a_b

@(posedge clk) a ## [1:$] b

endsequence

4.[*n]Operation symbol to indicate repetition. n Must be non negative, it cannot be $

//a pull up for one cycle, b pull up for two cycles

sequence

@(posedge clk) a ## 1 b[*2];

endsequence

5.[*m:n]To represent repeated events within a certain range

/*

a ##1 b ##1 b ||

a ##1 b ##1 b ##1 b ||

a ##1 b ##1 b ##1 b ##1 b ||

a ##1 b ##1 b ##1 b ##1 b ##1 b ||

*/

sequence a_b

@(posedge clk) a ## 1 b[*2:5]

endsequence

6.[=m] Used to indicate the continuity of an event, which needs to happen repeatedly m Times, but it does not need to occur in a continuous cycle

//b[=3] means that b must be 1 in 3 cycles, but it does not need to be 3 consecutive cycles

sequence a_b

@(posedge clk) a ## 1 b [=3];

endsequence

7.[=m:n]Indicates from minimum m To maximum n The number of discontinuous cycles that occur repeatedly

8.a[*0]Indicates that it is not valid for any positive clock cycle

| Symbol | meaning |

|---|

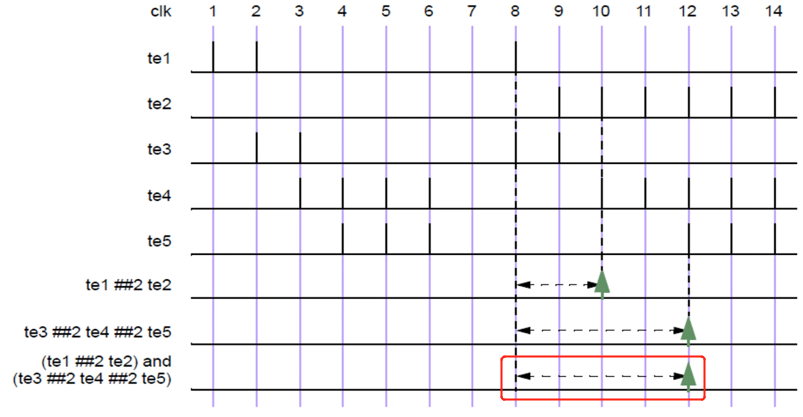

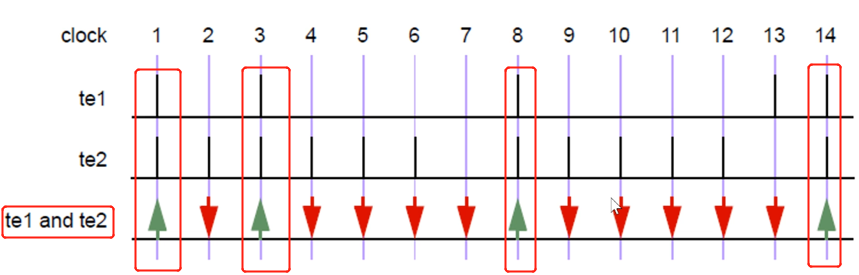

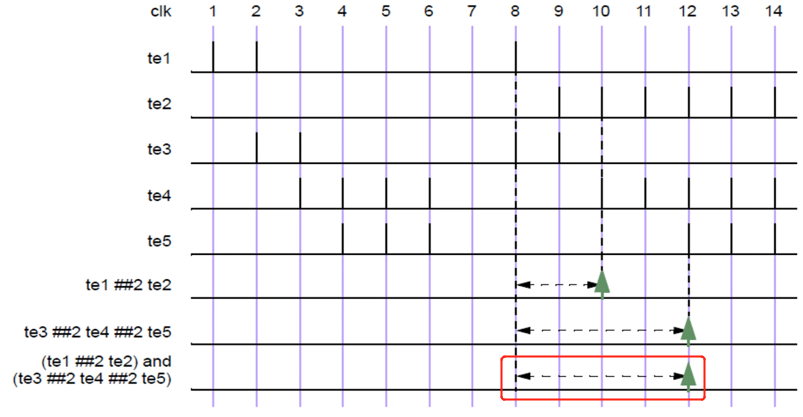

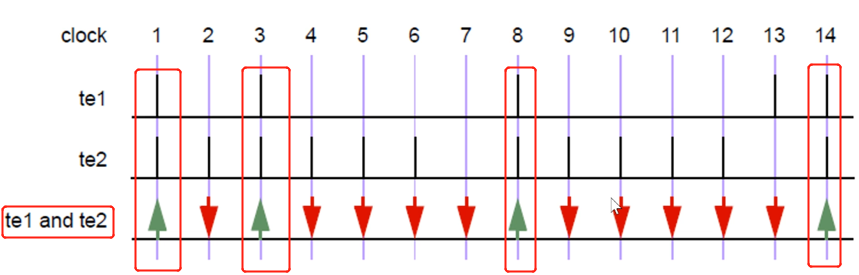

| and | Used to indicate that two sequences need to be matched; SEQ1 and SEQ2 |

The following conditions will satisfy this operation:

- After starting from the same starting point, seq1 and seq2 meet

- The time of satisfaction occurs in the period that both sequences meet, that is, the time of satisfaction of the later sequence

- The satisfaction time of the two sequences can be different

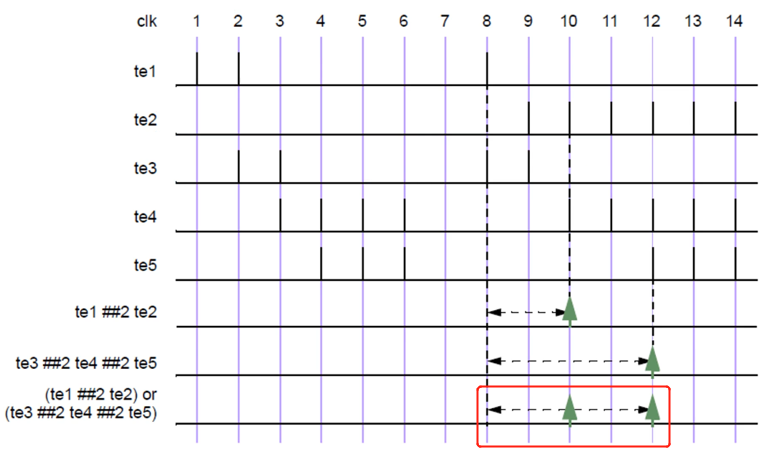

(te1 ##2 te2) and (te3 ##2 te4 ##2 te5)

If the sequences on both sides of the operator are used to measure the sampling signal rather than the event timing, it is required that the sequences on both sides of and should meet the conditions in the same period

| Symbol | meaning |

|---|

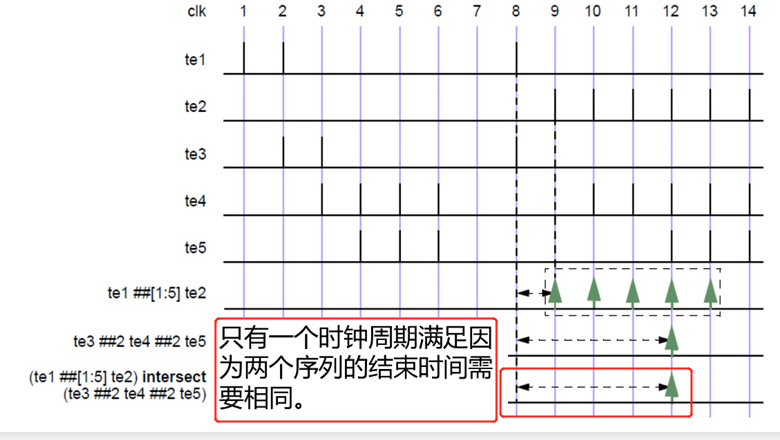

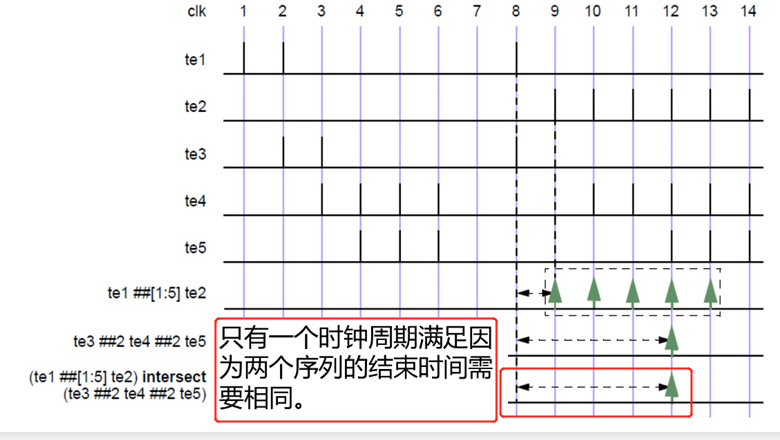

| intersect | Similar to the and operator, it only needs the sequence timing of both sides to match in the same clock cycle; SEQ1 intersect SEQ2 |

(te1 ## [1:5] te2) intersect (te3 ##2 te4 ##2 te5)

| Symbol | meaning |

|---|

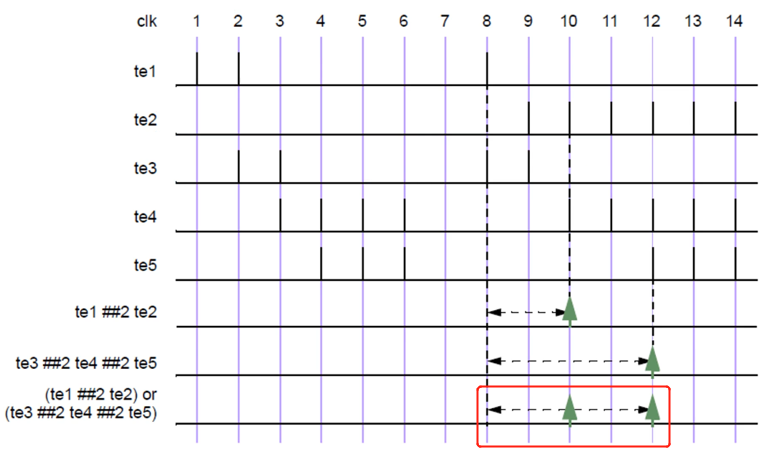

| OR | Used to indicate that at least one of the two sequences needs to be satisfied; SEQ1 or SEQ2 |

This operator is satisfied when:

- seq1 and seq2 are triggered from the same time

- Finally meet seq1 or seq2

- The end time of each sequence can be different, and the end time shall be subject to the last sequence time satisfied by the sequence

(te1 ##2 te2) or (te3 ##2 te4 ##2 te5)

//If the burst write length is 4, the write length can be 1, 2, or 4

property BurstLengthValid

@(posedge clk) disable iff (!rst)

((burstLen==4) |->

(wrlen==1) OR (wrlen==2) or (wrlen==4));

endproperty

assert property (BurstLengthValid)

| Symbol | meaning |

|---|

| first_match | Used to select the first satisfaction time from the multiple satisfaction sequence; first_match SEQ1 |

//t1 sequence can be used to match te1##te2,te1##3te2,te1##4te2 or te1##5te2

sequence t1;

te1 ## [2:5] te2;

endsequence

//This sequence is used to select the time of the first match

sequence ts1;

first_match(te1 ## [2:5] te2);

endsequence

| Symbol | meaning |

|---|

| throughout | Used to check whether a signal or an expression meets the requirements when running through a sequence; Sig throughout SEQ1 |

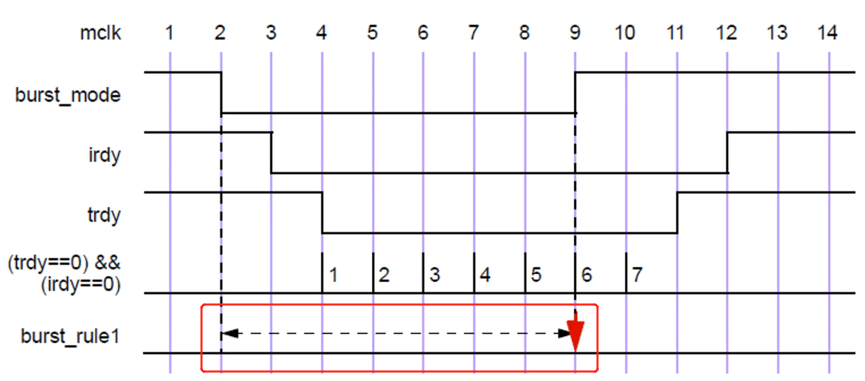

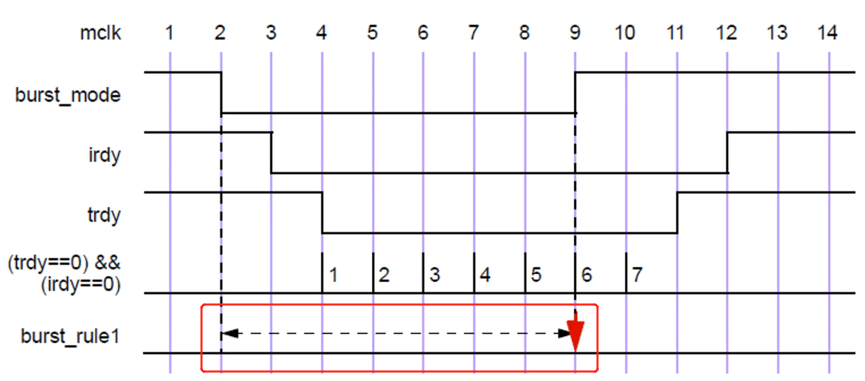

//irdy/trdy should be kept low for 7 consecutive cycles after the burst mode signal is pulled low for 2 cycles, and the burst mode signal should also be kept low for this consecutive cycle

sequence burst_rule1;

@(posedge mclk)

$fell(burst_mode) ##0

(!burst_mode) throughout (##2 ((trdy==0)&&(irdy)) [*7]);

endsequence

| Symbol | meaning |

|---|

| within | When seq1 is satisfied, it is established within a part of the continuous clock cycle of seq2; SEQ1 within SEQ2 |

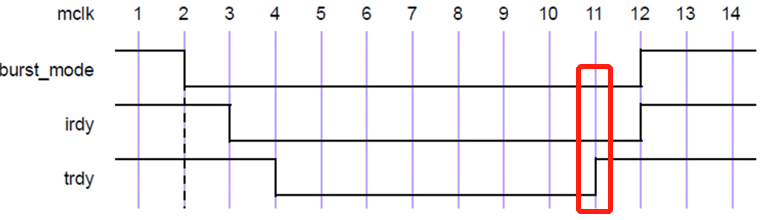

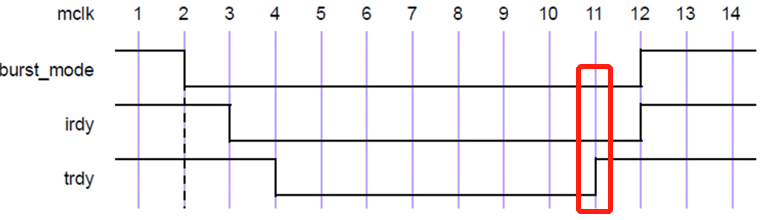

//trdy needs to keep 7 cycles low after one cycle pulled down by irdy, and irdy will also keep 8 cycles low. The following sequence will be met in the 11th clock cycle

!trdy[*7] within (($fell irdy) ##1 !irdy[*8])

You can use if in the sequence else

//When master_ When req is high, req1 or req2 should be high in the next cycle. If req1 is high, ack1 is high in the next cycle. If req2 is high, ack2 is high in the next cycle

property master_child_regs;

@(posedge clk) master_req ##1 (req1 || req2)

if(req1)

(##1 ack1)

else

(##1 ack2);

endproperty

//During cache access, if cache lookup is satisfied, the state machine state should be READ_CHACHE, otherwise it should be REQ_OUT

property cache_hit_check

@(posedge clk) (state==CACHE_LOOKUP) ##1 (CHit || CMiss) |->

if (CHit)

##1 (state==CACHE_READ);

else

##1 (state==REQ_OUT);

endproperty

assertion property(cache_hit_check) else $error;

| Symbol | meaning |

|---|

| SEQ.ended | At a certain time, if the sequence reaches the end in time |

//In the next cycle when inst is high, sequence e1 should end or has ended

sequence e1;

@(posedge sysclk) $rose(ready) ##1 process ##1 proc2;

endsequence

sequence rule;

@(posedge sysclk) reset ##1 inst ##1 e1.ended ##1 branch_back;

endsequence

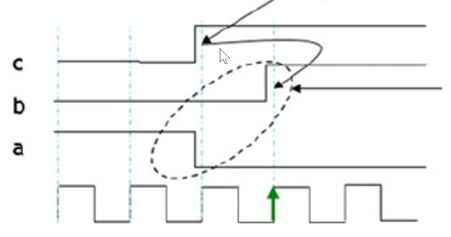

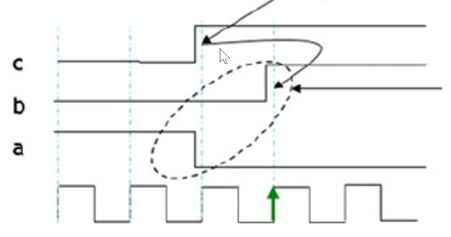

//In the next cycle of c pulling up, the sequence of a pulling down and b pulling up should also end

sequence aRbseq (aFell, bRose);

@(posedge clk) $fell(aFell) ##1

$rose(bRose);

endsequence

property endCycle;

@(posedge clk) $rose(c) |=>

aRbseq(a,b).ended

endproperty

2. Operator

| Symbol | meaning |

|---|

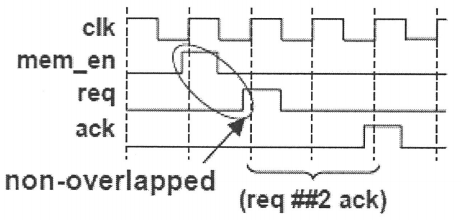

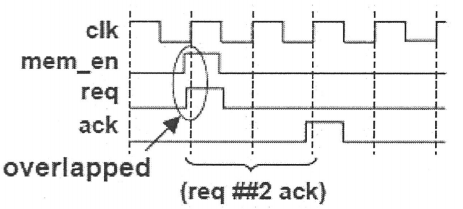

| I- > | Overlapping interleaving symbol |

- If the conditions are met, its subsequent operator sequence is evaluated

- If the conditions are not met, it will be null and successful, and the subsequent operators will not be executed

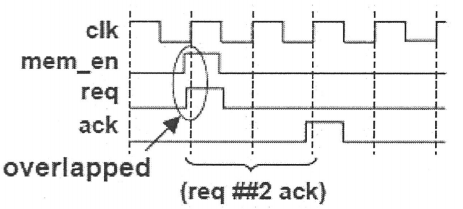

property p_req_ack;

@(posedge clk) mem_en |-> (req ##2 ack);

endproperty:p_req_ack

| Symbol | meaning |

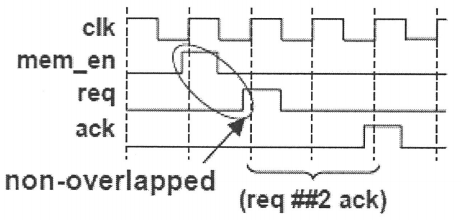

|---|

| I=> | Non overlapping interleaved symbol |

- If the conditions are met, its subsequent operator sequence is evaluated in the next cycle

- If the conditions are not met, it will be null and successful, and the subsequent operators will not be executed

3. Local variables

- Local variables can be used in sequence or property

- These variables will be created dynamically along with sequence and property

- Each sequence instance will have its own variable copy

//After the cache rdDone is raised, the read rdDate will be added with 1 after 2 cycles and written as wrData

sequence rd_cache_done;

##[1:5] rdDone;

endsequence;

sequence check_reg_wr_data;

int local_data;

(rd_cache_done, local_data=cache_rd_data) ##2 (reg_wr_data == (local_data+1));

endsequence

4. Call method

- When the sequence matches, you can call task, void function and system function

//At the end of the s1 sequence, the values when the e and f variables are sampled can be printed out respectively

sequence s1

logic v,w;

(a,v = e) ## 1

(b[->1], w = f, $display("b after a with v = %h, w = %h\n", v, w));

endsequence

| function | meaning |

|---|

| $rose() | Used to determine whether the lowest bit of the variable jumps to 1 compared with the previous sampling period |

| $fell() | Used to determine whether the lowest bit of the variable jumps to 0 compared with the previous sampling period |

| $stable() | Used to indicate that the value of the expression remains unchanged in two consecutive sampling periods |

| $pase() | Used to access values before several sampling periods in the past |

| $countbits(expression, control_bit) | Calculate matching control in expression_ Number of bits of bit value |

| $countones(expression) | Calculate the number of digits of 1 in expression |

| $onehot(expression) | Check whether there is and only 1 bit is 1 in expression |

| $isunknown(expression) | Check whether there is x or z in expression |

| $asserton | Default control, which is used to open all assertion s |

| $asseroff | Temporarily stop the operation of insertion |

| $assertkill | Terminate all executed assertion s |