preface

UVM is a methodology of IC Verification. The basic framework of verification environment built by UVM is similar. Therefore, the basic framework of verification environment of UVM can be generated through script. This paper mainly introduces a script uvmgen provided by synopsys in vcs tool. Through this script, a complete set of UVM verification environment can be automatically generated, or only one UVM component can be generated.

1, Use of uvmgen

First, use uvmgen this script to generate a complete UVM environment; Then run the environment to solve some compatibility problems between some systems, tools and UVM environment.

1.1 uvmgen generate a complete UVM environment

Here is how to generate a complete uvmgen environment through uvmgen this script.

hefei@ubuntu:~$ which uvmgen

/opt/synopsys/vcs_vO-2018.09-SP2/bin/uvmgen

hefei@ubuntu:~$ uvmgen

------------------------------------------------------------

WELCOME TO UVM TEMPLATE GENERATOR

------------------------------------------------------------

UVM templates compatible to UVM 1.1/1.2 used.

Using template from /opt/synopsys/vcs_vO-2018.09-SP2/etc/uvm_template/shared/lib/templates/uvm

1) Enter 1 to Create Complete Environment

2) Enter 2 to Generate Individual Template

Select [1-2]: 1

Do you want to create your own methods [Instead of UVM shorthand macros] ?

Select [ y/Y/n/N ][Default: n]: n

Would you be associating UVM REG models in your environment class? enter (y/n) [Default: n]:y

Enter Name of RAL Adapter:ral_ad1

Enter the environment name: top_env

Do you want to create Agents?

Select(y/Y/n/N) [Default: n]:y

Enter Master agent data

Enter name of master agent: mst

Enter name of sequencer: sqr1

Enter name of driver: drv1

Enter name of monitor: mon1

Enter name of interface: intf1

Enter name of the transaction: tr1

Is this transaction class extended from a BU class? enter (y/n): n

Enter Slave agent data

Enter name of slave agent: slv

Enter name of sequencer: sqr2

Enter name of driver: drv2

Enter name of monitor: mon2

Enter name of interface: intf2

Do you want to use same transaction class for master and slave agents ? enter (y/n):y

Choose one of the following ral bfm:

1) RAL sequence adapter, single domain

2) RAL sequence adapter, multiplexed domains

select [1-2]:2

Enter Name of second RAL Adapter:ral_ad2

Enter Driver information for the slave agent slv ::

Choose one of following driver available

1) Driver, PUSH DRIVER (uvm_push_driver)

2) Driver, PULL DRIVER (uvm_driver)

Select [1- 2] [Default: 2]:

Enter Driver information for the master agent mst ::

Choose one of following driver available

1) Driver, PUSH DRIVER (uvm_push_driver)

2) Driver, PULL DRIVER (uvm_driver)

Select [1- 2] [Default: 2]:

Would you like to implement scoreboard?

Select(y/Y/n/N) [Default: y]:y

Enter Name of Scoreboard Class:scb

The testcase generated is top_env_test

------------------------------------------------------------

Template generation completed.

------------------------------------------------------------

Usage notes :

1) Find the generated files in "proj/top_env" directory.

2) Makefile has been placed in run "proj/top_env/run" directory.

3) Edit files and look for comments marked "ToDo:" and fill

in the application-specific behavior for your function.

------------------------------------------------------------

After executing the above script, a proj folder will be generated in the executed directory. The hierarchy of the folder is as follows:

hefei@ubuntu:~/proj$ tree . ├── README ├── top_env │ ├── doc │ ├── env │ │ ├── mst.sv │ │ ├── slv.sv │ │ ├── top_env_ral_env.sv │ │ └── top_env.ralf │ ├── examples │ ├── hdl │ │ └── top_env_top.sv │ ├── include │ │ ├── mstr_slv_intfs.incl │ │ ├── mstr_slv_src.incl │ │ └── top_env.sv │ ├── run │ │ └── Makefile │ ├── src │ │ ├── mon_2cov.sv │ │ ├── mst_drv1.sv │ │ ├── mst_intf1.sv │ │ ├── mst_mon1.sv │ │ ├── mst_sequence_library.sv │ │ ├── mst_sqr1.sv │ │ ├── mst_tr1.sv │ │ ├── ral_multiplexed.sv │ │ ├── scb.sv │ │ ├── slv_drv2.sv │ │ ├── slv_intf2.sv │ │ ├── slv_mon2.sv │ │ ├── slv_sqr2.sv │ │ ├── slv_tr1.sv │ │ ├── top_env_cfg.sv │ │ └── top_env_cov.sv │ └── tests │ ├── top_env_tb_mod.sv │ └── top_env_test.sv └── uvmgen_options_log.txt

1.2 solve the problem of operation error reporting

Go directly to proj / top_ The env / run folder will report the following error after executing make. This is because our system is 64 bit, and the - full64 option is not added when executing ralgen and vcs.

hefei@ubuntu:~/proj/top_env/run$ make

rm -rf simv* csrc

rm -rf vc_hdrs.h .vcsmx_rebuild *.log

rm -rf work/* *.svshell vcs_version

cd ../env; ralgen -uvm -l sv -t top_env -c b -c a -c f top_env.ralf;cd -

Error: Bad VMM installation. Executable 'ralgen.binary' not visible.

/home/hefei/proj/top_env/run

vcs -sverilog -l vcs.log -debug_pp +incdir+/opt/uvm-1.2/src /opt/uvm-1.2/src/uvm_pkg.sv /opt/uvm-1.2/src/dpi/uvm_dpi.cc -CFLAGS -DVCS +incdir+../include+../src+../env+../tests+../hdl \

../tests/top_env_tb_mod.sv ../hdl/top_env_top.sv

Error-[VCS_COM_UNE] Cannot find VCS compiler

VCS compiler not found. Environment variable VCS_HOME

(/opt/synopsys/vcs_vO-2018.09-SP2/linux) is selecting a directory in which

there isn't a compiler '/opt/synopsys/vcs_vO-2018.09-SP2/linux/bin/vcs1' for

a machine of this type 'linux'.

Please check whether 'VCS_HOME' is incorrect; if not, see below.

Perhaps vcs hasn't been installed for machine of type "linux".

Or the installation has been damaged.

To verify whether vcsO-2018.09 supports machine of type "Linux 5.4.0-77-generic",

please look at ReleaseNotes for more details .

We determine the machine type from uname; maybe uname is incorrect.

You can fix installation problems by reinstalling from CDROM

or downloading it from the Synopsys ftp server.

For assistance, please contact vcs technical support

at vcs_support@synopsys.com or call 1-800-VERILOG

Makefile:61: recipe for target 'comp' failed

make: *** [comp] Error 1

Open the Makefile file and select comp on line 41_ After opts and 61 lines of ralgen, add the - full64 option respectively, as shown in the following code.

COMP_OPTS = -full64 -sverilog -l vcs.log $(UVM) $(INCL) $(DEFINES) cd ../env; ralgen -full64 -uvm -l sv -t top_env -c b -c a -c f top_env.ralf;cd -

Libvcsnew encountered after re make So: undefined reference to the problem, you can refer to the following link to solve it.

libvcsnew.so: undefined reference to

After adding the - LDFLAGS -Wl, - no as needed option, the code is as follows:

COMP_OPTS = -full64 -sverilog -LDFLAGS -Wl,--no-as-needed -l vcs.log $(UVM) $(INCL) $(DEFINES)

After making again, the simulation log is as follows:

./simv -l simv.log \

+ntb_random_seed=1 +UVM_TESTNAME=top_env_test

Chronologic VCS simulator copyright 1991-2018

Contains Synopsys proprietary information.

Compiler version O-2018.09-SP2_Full64; Runtime version O-2018.09-SP2_Full64; Jun 24 19:47 2021

UVM_INFO /opt/uvm-1.2/src/base/uvm_root.svh(392) @ 0: reporter [UVM/RELNOTES]

----------------------------------------------------------------

UVM-1.2

(C) 2007-2014 Mentor Graphics Corporation

(C) 2007-2014 Cadence Design Systems, Inc.

(C) 2006-2014 Synopsys, Inc.

(C) 2011-2013 Cypress Semiconductor Corp.

(C) 2013-2014 NVIDIA Corporation

----------------------------------------------------------------

*********** IMPORTANT RELEASE NOTES ************

You are using a version of the UVM library that has been compiled

with `UVM_NO_DEPRECATED undefined.

See http://www.eda.org/svdb/view.php?id=3313 for more details.

You are using a version of the UVM library that has been compiled

with `UVM_OBJECT_DO_NOT_NEED_CONSTRUCTOR undefined.

See http://www.eda.org/svdb/view.php?id=3770 for more details.

(Specify +UVM_NO_RELNOTES to turn off this notice)

UVM_INFO @ 0: reporter [RNTST] Running test top_env_test...

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

Note-[FCICIO] Instance coverage is ON

/home/hefei/proj/top_env/run/../env/ral_top_env.sv, 161

top_env_tb_mod, "top_env_tb_mod::ral_block_top_env::cg_addr"

Instance coverage is set (option.per_instance = 1) for covergroup

'top_env_tb_mod::ral_block_top_env::cg_addr'

Covergroup Instance: me.obj.cg_addr

Design hierarchy: top_env_top.test

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

Note-[FCICIO] Instance coverage is ON

/home/hefei/proj/top_env/run/../env/ral_top_env.sv, 14

top_env_tb_mod, "top_env_tb_mod::ral_reg_top_env_CHIP_ID::cg_bits"

Instance coverage is set (option.per_instance = 1) for covergroup

'top_env_tb_mod::ral_reg_top_env_CHIP_ID::cg_bits'

Covergroup Instance: me.obj.cg_bits

Design hierarchy: top_env_top.test

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

UVM_INFO /opt/uvm-1.2/src/base/uvm_root.svh(579) @ 0: reporter [UVMTOP] UVM testbench topology:

--------------------------------------------------------------------------

Name Type Size Value

--------------------------------------------------------------------------

uvm_test_top top_env_test - @423

env top_env_ral_env - @436

cov top_env_cov - @467

Coverage Analysis uvm_analysis_imp - @476

master_agent mst - @449

mast_drv drv1 - @688

rsp_port uvm_analysis_port - @707

seq_item_port uvm_seq_item_pull_port - @697

mast_mon mon1 - @532

mon_analysis_port uvm_analysis_port - @541

mast_sqr sqr1 - @551

rsp_export uvm_analysis_export - @560

seq_item_export uvm_seq_item_pull_imp - @678

arbitration_queue array 0 -

lock_queue array 0 -

num_last_reqs integral 32 'd1

num_last_rsps integral 32 'd1

mon2cov mon1_2cov_connect - @486

sb scb - @495

after_export uvm_analysis_export - @736

before_export uvm_analysis_export - @726

comparator uvm_in_order_class_comparator #(T) - @746

after uvm_tlm_analysis_fifo #(T) - @844

analysis_export uvm_analysis_imp - @893

get_ap uvm_analysis_port - @883

get_peek_export uvm_get_peek_imp - @863

put_ap uvm_analysis_port - @873

put_export uvm_put_imp - @853

after_export uvm_analysis_export - @765

before uvm_tlm_analysis_fifo #(T) - @785

analysis_export uvm_analysis_imp - @834

get_ap uvm_analysis_port - @824

get_peek_export uvm_get_peek_imp - @804

put_ap uvm_analysis_port - @814

put_export uvm_put_imp - @794

before_export uvm_analysis_export - @755

pair_ap uvm_analysis_port - @775

slave_agent slv - @458

drv drv2 - @923

rsp_port uvm_analysis_port - @942

seq_item_port uvm_seq_item_pull_port - @932

mon mon2 - @904

mon_analysis_port uvm_analysis_port - @913

slv_seqr sqr2 - @952

rsp_export uvm_analysis_export - @961

seq_item_export uvm_seq_item_pull_imp - @1079

arbitration_queue array 0 -

lock_queue array 0 -

num_last_reqs integral 32 'd1

num_last_rsps integral 32 'd1

--------------------------------------------------------------------------

UVM_INFO /opt/uvm-1.2/src/base/uvm_factory.svh(1645) @ 0: reporter [UVM/FACTORY/PRINT]

#### Factory Configuration (*)

No instance or type overrides are registered with this factory

All types registered with the factory: 80 total

Type Name

---------

REGTR

base_sequence

drv1

drv2

mon1

mon1_2cov_connect

mon2

mst

ral_ad2

ral_block_top_env

ral_mem_top_env_top_env_RAM

ral_reg_top_env_CHIP_ID

reg_seq

scb

sequence_0

sequence_1

slv

sqr1

sqr1_sequence_library

sqr2

top_env_cfg

top_env_cov

top_env_ral_env

top_env_test

tr1

(*) Types with no associated type name will be printed as <unknown>

####

UVM_INFO ../src/mst_drv1.sv(121) @ 0: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_mon1.sv(133) @ 0: uvm_test_top.env.master_agent.mast_mon [top_env_MONITOR] Starting transaction...

UVM_INFO ../src/mst_mon1.sv(137) @ 0: uvm_test_top.env.master_agent.mast_mon [top_env_MONITOR] User need to add monitoring logic

$finish called from file "../src/mst_mon1.sv", line 138.

$finish at simulation time 0

V C S S i m u l a t i o n R e p o r t

Time: 0

CPU Time: 1.110 seconds; Data structure size: 0.4Mb

So far, the whole UVM environment generated by uvmgen script has been able to run normally.

Uvmgen can also generate a single UVM component and quickly generate a complete UVM environment. For more information on the use of uvmgen scripts, please refer to the following documents.

2, uvmgen generated UVM environment

To get this environment, first of all, the first idea is to print the waveform of the interface to see if the clock reset is correct; Secondly, to solve the problem of abnormal end of simulation, the log of simulation execution above shows that $finish called from file "... / src/mst_mon1.sv", line 138, This is not the log of the normal end of UVM simulation.

2.1 add print waveform

Open the top-level file proj/top_env/hdl/top_env_top.sv, add the following code to print the waveform.

initial

$fsdbDumpvars();

For the Undefined System Task call to '$fsdbDumpfile' problem encountered after making again, the solution is as follows:

Undefined System Task call to '$fsdbDumpfile'

After that, turn on the fsdb waveform, call out the clock and reset signal, and the display is normal. There is no bug as described below. Although the VCS versions are different, the source codes generated by clock reset are consistent.

The 2011 VCS comes with a BUG in UVMGEN. It's hard to imagine such a BUG ~ ~

2.2 solve the problem of abnormal end of simulation

The log of simulation execution shows that $finish called from file "... / src/mst_mon1.sv", line 138, This is not the normal end log of UVM simulation, and the corresponding sequence excitation is not issued.

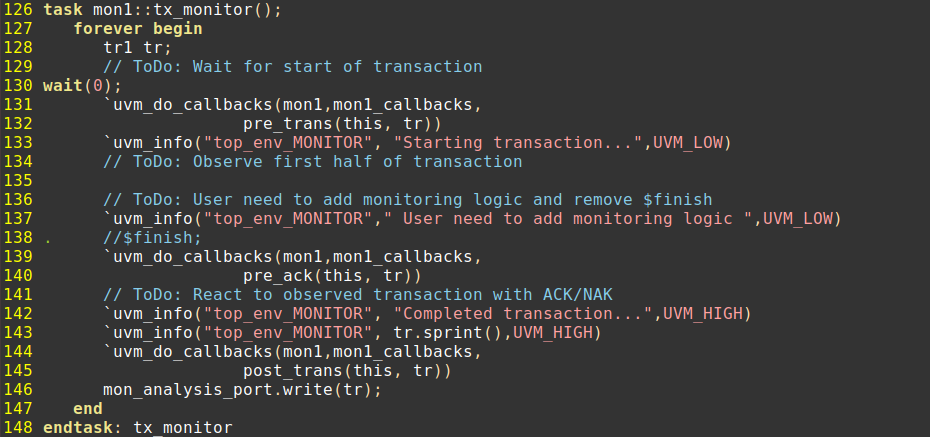

Open proj/top_env/src/mst_mon1.sv, locate line 138, mask the finish in line 138, and add a wait(0) in line 130 to prevent the forever loop in mon1 from brushing the log all the time (this is only a temporary treatment, which needs to be removed when filling in the code later), as shown in the following figure.

Handle proj / top in the same way_ env/src/slv_ mon2. SV file.

make again. Through the following log, you can see that the simulation has ended normally and the excitation in the sequence has been distributed to the drver.

./simv -l simv.log \

+ntb_random_seed=1 +UVM_TESTNAME=top_env_test

Chronologic VCS simulator copyright 1991-2018

Contains Synopsys proprietary information.

Compiler version O-2018.09-SP2_Full64; Runtime version O-2018.09-SP2_Full64; Jun 25 00:02 2021

UVM_INFO /opt/uvm-1.2/src/base/uvm_root.svh(392) @ 0: reporter [UVM/RELNOTES]

----------------------------------------------------------------

UVM-1.2

(C) 2007-2014 Mentor Graphics Corporation

(C) 2007-2014 Cadence Design Systems, Inc.

(C) 2006-2014 Synopsys, Inc.

(C) 2011-2013 Cypress Semiconductor Corp.

(C) 2013-2014 NVIDIA Corporation

----------------------------------------------------------------

*********** IMPORTANT RELEASE NOTES ************

You are using a version of the UVM library that has been compiled

with `UVM_NO_DEPRECATED undefined.

See http://www.eda.org/svdb/view.php?id=3313 for more details.

You are using a version of the UVM library that has been compiled

with `UVM_OBJECT_DO_NOT_NEED_CONSTRUCTOR undefined.

See http://www.eda.org/svdb/view.php?id=3770 for more details.

(Specify +UVM_NO_RELNOTES to turn off this notice)

UVM_INFO @ 0: reporter [RNTST] Running test top_env_test...

*Verdi* Loading libsscore_vcs201809.so

FSDB Dumper for VCS, Release Verdi_O-2018.09-SP2, Linux x86_64/64bit, 02/21/2019

(C) 1996 - 2019 by Synopsys, Inc.

*Verdi* FSDB WARNING: The FSDB file already exists. Overwriting the FSDB file may crash the programs that are using this file.

*Verdi* : Create FSDB file 'novas.fsdb'

*Verdi* : Begin traversing the scopes, layer (0).

*Verdi* : End of traversing.

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

Note-[FCICIO] Instance coverage is ON

/home/hefei/proj/top_env/run/../env/ral_top_env.sv, 161

top_env_tb_mod, "top_env_tb_mod::ral_block_top_env::cg_addr"

Instance coverage is set (option.per_instance = 1) for covergroup

'top_env_tb_mod::ral_block_top_env::cg_addr'

Covergroup Instance: me.obj.cg_addr

Design hierarchy: top_env_top.test

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

Note-[FCICIO] Instance coverage is ON

/home/hefei/proj/top_env/run/../env/ral_top_env.sv, 14

top_env_tb_mod, "top_env_tb_mod::ral_reg_top_env_CHIP_ID::cg_bits"

Instance coverage is set (option.per_instance = 1) for covergroup

'top_env_tb_mod::ral_reg_top_env_CHIP_ID::cg_bits'

Covergroup Instance: me.obj.cg_bits

Design hierarchy: top_env_top.test

UVM_INFO /opt/uvm-1.2/src/base/uvm_spell_chkr.svh(123) @ 0: reporter [UVM/CONFIGDB/SPELLCHK] include_coverage not located, did you mean default_sequence

UVM_INFO /opt/uvm-1.2/src/base/uvm_root.svh(579) @ 0: reporter [UVMTOP] UVM testbench topology:

--------------------------------------------------------------------------

Name Type Size Value

--------------------------------------------------------------------------

uvm_test_top top_env_test - @423

env top_env_ral_env - @436

cov top_env_cov - @467

Coverage Analysis uvm_analysis_imp - @476

master_agent mst - @449

mast_drv drv1 - @688

rsp_port uvm_analysis_port - @707

seq_item_port uvm_seq_item_pull_port - @697

mast_mon mon1 - @532

mon_analysis_port uvm_analysis_port - @541

mast_sqr sqr1 - @551

rsp_export uvm_analysis_export - @560

seq_item_export uvm_seq_item_pull_imp - @678

arbitration_queue array 0 -

lock_queue array 0 -

num_last_reqs integral 32 'd1

num_last_rsps integral 32 'd1

mon2cov mon1_2cov_connect - @486

sb scb - @495

after_export uvm_analysis_export - @736

before_export uvm_analysis_export - @726

comparator uvm_in_order_class_comparator #(T) - @746

after uvm_tlm_analysis_fifo #(T) - @844

analysis_export uvm_analysis_imp - @893

get_ap uvm_analysis_port - @883

get_peek_export uvm_get_peek_imp - @863

put_ap uvm_analysis_port - @873

put_export uvm_put_imp - @853

after_export uvm_analysis_export - @765

before uvm_tlm_analysis_fifo #(T) - @785

analysis_export uvm_analysis_imp - @834

get_ap uvm_analysis_port - @824

get_peek_export uvm_get_peek_imp - @804

put_ap uvm_analysis_port - @814

put_export uvm_put_imp - @794

before_export uvm_analysis_export - @755

pair_ap uvm_analysis_port - @775

slave_agent slv - @458

drv drv2 - @923

rsp_port uvm_analysis_port - @942

seq_item_port uvm_seq_item_pull_port - @932

mon mon2 - @904

mon_analysis_port uvm_analysis_port - @913

slv_seqr sqr2 - @952

rsp_export uvm_analysis_export - @961

seq_item_export uvm_seq_item_pull_imp - @1079

arbitration_queue array 0 -

lock_queue array 0 -

num_last_reqs integral 32 'd1

num_last_rsps integral 32 'd1

--------------------------------------------------------------------------

UVM_INFO /opt/uvm-1.2/src/base/uvm_factory.svh(1645) @ 0: reporter [UVM/FACTORY/PRINT]

#### Factory Configuration (*)

No instance or type overrides are registered with this factory

All types registered with the factory: 80 total

Type Name

---------

REGTR

base_sequence

drv1

drv2

mon1

mon1_2cov_connect

mon2

mst

ral_ad2

ral_block_top_env

ral_mem_top_env_top_env_RAM

ral_reg_top_env_CHIP_ID

reg_seq

scb

sequence_0

sequence_1

slv

sqr1

sqr1_sequence_library

sqr2

top_env_cfg

top_env_cov

top_env_ral_env

top_env_test

tr1

(*) Types with no associated type name will be printed as <unknown>

####

UVM_INFO ../src/mst_drv1.sv(121) @ 0: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/slv_drv2.sv(121) @ 0: uvm_test_top.env.slave_agent.drv [top_env_DRIVER] Starting transaction...

UVM_INFO /opt/uvm-1.2/src/seq/uvm_sequence_library.svh(659) @ 0: uvm_test_top.env.master_agent.mast_sqr@@sqr1_sequence_library [SEQLIB/START] Starting sequence library sqr1_sequence_library in main phase: 10 iterations in mode UVM_SEQ_LIB_RAND

UVM_INFO ../src/mst_drv1.sv(137) @ 0: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 0: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 1900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 1900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2100: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2200: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2300: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2400: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2500: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2600: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2700: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2800: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 2900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 2900: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO ../src/mst_drv1.sv(137) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Completed transaction...

UVM_INFO ../src/mst_drv1.sv(121) @ 3000: uvm_test_top.env.master_agent.mast_drv [top_env_DRIVER] Starting transaction...

UVM_INFO /opt/uvm-1.2/src/seq/uvm_sequence_library.svh(736) @ 3000: uvm_test_top.env.master_agent.mast_sqr@@sqr1_sequence_library [SEQLIB/END] Ending sequence library in phase main

UVM_INFO ../src/scb.sv(50) @ 3000: uvm_test_top.env.sb [SBRPT] Matches = 0, Mismatches = 0

UVM_INFO /opt/uvm-1.2/src/base/uvm_report_server.svh(847) @ 3000: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 212

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[RNTST] 1

[SBRPT] 1

[SEQLIB/END] 1

[SEQLIB/START] 1

[UVM/CONFIGDB/SPELLCHK] 3

[UVM/FACTORY/PRINT] 1

[UVM/RELNOTES] 1

[UVMTOP] 1

[top_env_DRIVER] 202

$finish called from file "/opt/uvm-1.2/src/base/uvm_root.svh", line 517.

$finish at simulation time 3000

V C S S i m u l a t i o n R e p o r t

Time: 3000

CPU Time: 1.350 seconds; Data structure size: 0.5Mb

So far, the UVM environment framework generated by uvmgen script has been compiled and simulated normally. What we need to do next is to fill the specific implementation into the corresponding components according to our own project. The components to be modified include driver, monitor, sequence, regmodel, coverage, etc.

2.3 some problems found in the environment

Problem 1: the monitor component cannot get the interface.

Whether it is the monitor component in mst or slv, on the one hand, the tag used in get is inconsistent with the previous set, resulting in no interface for get; On the other hand, there is no need to judge whether the obtained handle is empty.

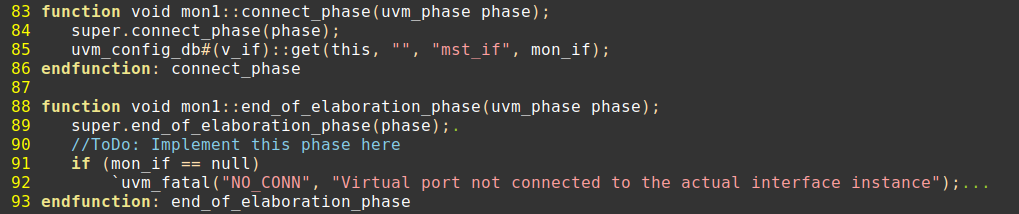

Modify MST_ The code of mon1 is as follows:

There are two main modifications: 1. The third parameter label of the get function in line 85 is marked by mon_ Change if to mst_if; 2. Add lines 91 and 92 to detect MST_ Whether to get the interface in mon1. If not, end the simulation immediately.

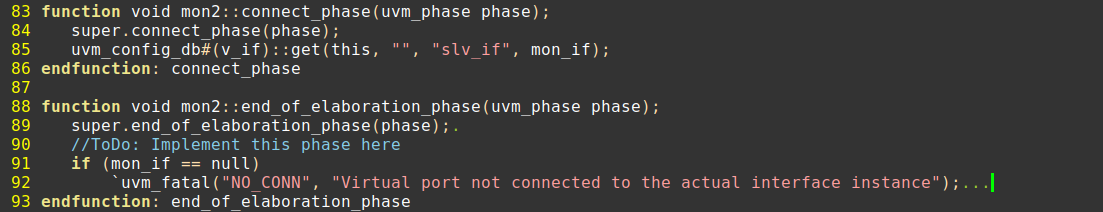

slv_ Code modification method of mon2 and MST_ Similar to mon1, the label is changed to slv_if.

For the location of set tasks corresponding to these get tasks, please refer to the following posts:

How to locate UVM_ config_ Source of DB get task

In general, the get tasks in agt, drv and mon come from proj / top_ env/tests/top_ env_ tb_ mod. For the two set tasks in lines 19 and 20 in SV, when the first two parameters of the set task are empty, it should be set in the whole domain. Therefore, this interface can be obtained in uvm all places.

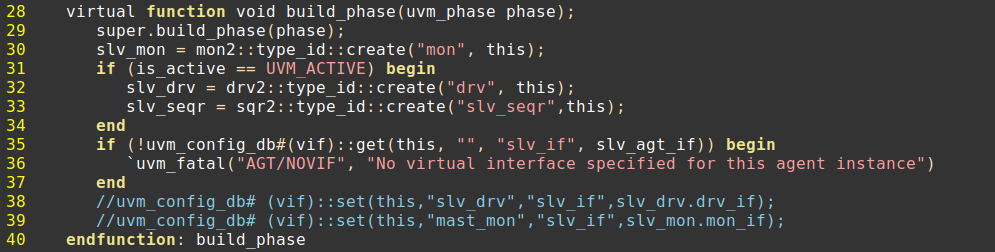

Finally, you need to set proj/top_env/env/mst.sv and proj / top_ env/env/slv. Lines 38 and 39 of SV are commented out, as shown in the figure below. This is because the set function has no meaning to pass its own interface to itself, and it passes + UVM during simulation_ CONFIG_ DB_ After trace adds this macro, it will also debug and report an error.

summary

Firstly, this paper records the method of using uvmgen script to generate a complete UVM verification environment framework; Then the compatibility between some systems, tools and UVM environment is solved; Finally, it is found and solved that in the framework of UVM verification environment generated by script, through config_ The problem of DB passing interface.