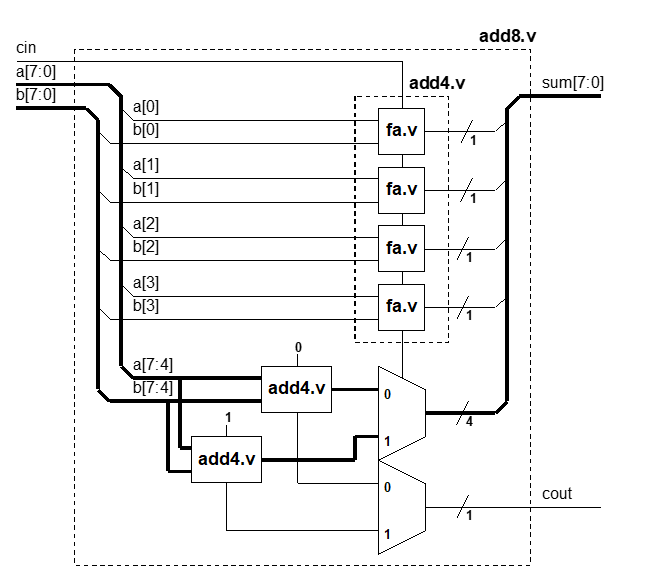

The main exercise in lab2 is to use ucli. The structure diagram of the adder of lab2 is shown in the figure below:

Bugs have been embedded in the tutorial files this time. What the tutorial does is the whole process of de bug ging.

PartA and PartB use the methods of modifying source files and using ucli respectively.

PartA

1. First, enter. / lab2/parta under the general directory, and use the. f file to run the command:

$ vcs –f adder.f -R

The compilation passed successfully, but there was an error in the simulation process:

***ERROR at time = 25750 *** a = 01, b = 01, sum = 00; cin = 0, cout = 0

You should get sum=02 here, and now you need to find out the cause of the error.

2.Verilog system task call

verilog's task call can be placed in RTL module code or testbench. In the actual debug ging process, the better choice is to put task call in testbench. I would like to have two:

(1) testbench is used to verify program results. It is easier to set breakpoints after using task call.

(2) it can avoid repeated compilation and omit resources and time.

Now let's use the more command to view the contents of the addertb.v file:

$ more addertb.v

module addertb;

reg [7:0] a_test, b_test;

wire [7:0] sum_test;

reg cin_test;

wire cout_test;

reg [17:0] test;

add8 u1(a_test, b_test, cin_test, sum_test, cout_test); //Example of DUT(Device Under Test)

initial

if (!$test$plusargs("monitoroff")) //Determine whether there is a "monitoroff" field in the entered command

$monitor ($time, " %h + %h = %h; cin = %h, cout = %h",

a_test, b_test, sum_test, cin_test, cout_test);//If not, start the monitoring process

initial

begin

for (test = 0; test <= 18'h1ffff; test = test +1) begin

cin_test = test[16];

a_test = test[15:8];

b_test = test[7:0];

#50;

if ({cout_test, sum_test} !== (a_test + b_test + cin_test)) begin

$display("***ERROR at time = %0d ***", $time); //Display time and data information when an error occurs

$display("a = %h, b = %h, sum = %h; cin = %h, cout = %h",

a_test, b_test, sum_test, cin_test, cout_test);

$finish; //End the simulation when an error is detected, equivalent to an endpoint

end

#50;

end

$display("*** Testbench Successfully completed! ***");

$finish;//Form a good habit of inserting simulation completion information. If the information does not pop up, it may indicate that the program has entered an infinite loop.

end

endmodule

The detailed explanation of several task call s is as follows:

- $display provides the ability to display strings and multiple parameter values.

- $monitor provides the ability to monitor and output expressions and variable values in parameter lists. When you start a $monitor task with one or more parameters, the value of the variable or expression in the entire parameter list will be output whenever the value of the variable or expression in the parameter list changes. If the value of two or more expressions changes at the same time, only output once. The parameter can be $time to indicate the time of change.

- $time represents the current time

- $finish means stop simulation

- When $test$plusargs is used, the function will determine whether the parameter string is defined and return 0 or non-0. For example, this example is used to determine whether "monitoroff" is "defined" in the command (in fact, whether this option is enabled).

reference material: https://blog.csdn.net/kevindas/article/details/80380144

https://www.cnblogs.com/pengwangguoyh/articles/3167498.html

3. Insert a new $display into the simulation code to trace the source of the error.

if ({cout_test, sum_test} !== (a_test + b_test + cin_test)) begin

$display("***ERROR at time = %0d ***", $time);

$display("a = %h, b = %h, sum = %h; cin = %h, cout = %h",

a_test, b_test, sum_test, cin_test, cout_test);

$display("\nIn add4(u1)"); //Newly added

$display("a = %b, b = %b, sum = %b; cin = %b, cout = %b",//Newly added

u1.a, u1.b, u1.sum, u1.cin, u1.cout);

$finish;